- 8 (812) 612-97-27

- СПБ, Курчатова дом 1А помещение 1Н

- order@das-elektro.de

ПОСТРОЕНИЕ АНАЛОГОВОГО ИЗМЕРИТЕЛЬНОГО ТРАКТА

В статье описаны некоторые проблемы, которые могут возникнуть при проектировании аналогового измерительного тракта. Памятуя об особенности рубрики «теория и практика», мы постарались обратить внимание на самые сложные вопросы. Поскольку эта публикация не претендует на роль обучающей из вузовского учебника, мы не стали описывать во всех подробностях, например, принцип действия АЦП, но упомянули лишь основные моменты, необходимые для понимания последующего изложения материала.

Введение

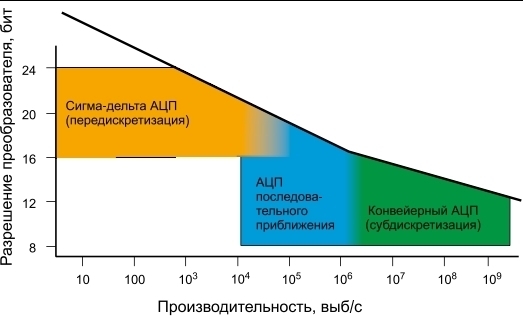

Мы живем в аналоговом мире. Чтобы воспринимаемая информация оказалась в цифровом виде, ее следует преобразовать. Эту задачу выполняет аналого-цифровой преобразователь. На протяжении многих лет видное место занимали три топологии – АЦП последовательного приближения,сигма-дельта() АЦП и конвейерный АЦП. Все три топологии в корне отличаются друг от друга и работают в разных частотных диапазонах в очень широком ряде приложений, начиная с низкочастотных датчиков и заканчивая высокочастотными лидарами или спутниковой связью. Помимо АЦП для преобразования сигналов необходим предварительный аналоговый тракт для усиления и формирования полосы пропускания сигналов. Мы кратко рассмотрим его основные функции. При описании АЦП мы частично опирались на [1–3].

Рисунок 1

Рисунок 2

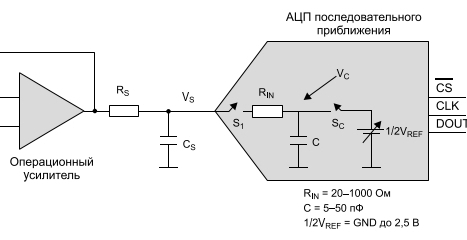

Упрощенная схема входного каскада АЦП последовательного приближения и оконечного усилителя аналогового тракта

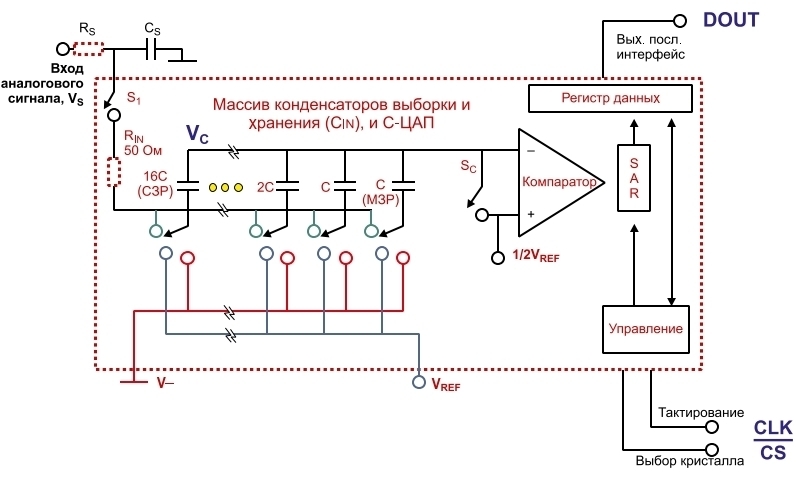

Схема 4-бит АЦП последовательного приближения

АЦП последовательного приближения

Начнем обзор с АцП последовательного приближения. Преобразователи этого вида появились первыми. Они продолжают занимать господствующее положение. Например, практически во всех микроконтроллерах (МК) встроенные АЦП являются преобразователи с последовательным приближением. Обычно разрядность АЦП последовательного приближения находится в пределах 8–18 бит, а производительность достигает 15 Мвыб/с. Важной особенностью АЦП последовательного приближения является возможность очень быстро осуществлять преобразование аналогового сигнала, благодаря чему при использовании многоканальных АЦП можно получать данные, относящиеся к одному моменту времени.

упрощенная схема входного каскада АЦП последовательного приближения и оконечного усилителя аналогового тракта показана на рисунке 1. Входной каскад АЦП содержит ключ входного сигнала (S1), емкостную матрицу, ключ преобразователя (SC) и источник опорного напряжения (½VREF).

Работа каскада АЦП последовательного приближения выглядит следующим образом.

1. Ключ S1 размыкается, SC замыкается. Такое переключение отсоединяет вход АЦП от источника аналогового сигнала.

2. Заряд на C повторно калибруется по источнику опорного напряжения ½VREF. Эта повторная калибровка возвращает АЦП в нулевую точку.

3. Ключ S1 замыкается, SC размыкается. Теперь устройство подключено к входному аналоговому сигналу.

4. АЦП принимает входной сигнал VS в течение заданного времени. Это время приема позволяет исключить шум переключения S1 и SC и внезапное воздействие усилителя на емкостную нагрузку.

5. Затем открываетс я S1: это тот момент, когда происходит моментальная фиксация уровня сигнала.

6. АЦП последовательного приближения преобразует сигнал VC в его цифровое представление. Время, необходимое для этого, называется «временем преобразования».

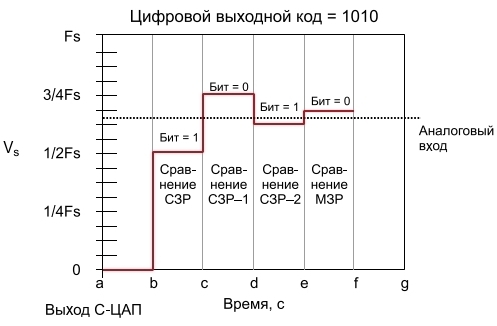

Структурная схема АЦП показана на рисунке 2, а временная диаграмма его работы – на рисунке 3. На первом этапе преобразования АЦП определяет старший бит, который в русскоязычной литературе называется старшим значащим разрядом (СЗР). Выполняется сравнение уровня сигнала с ½VREF путем коммутации нижней обкладки конденсатора 16C между входами компаратора V– и VREF. Затем выполняется сравнение с опорным сигналом ½VREF конденсатора 8C (на рисунке 2 не показан), за которым следует сравнение с 4C и т. д. Преобразование входного сигнала идет последовательно – разряд за разрядом. По этой причине АЦП последовательного приближения иногда называют АЦП с поразрядным взвешиванием. Полученное значение старшего бита передается через выход DOUT; ключ СЗР не меняет свое состояние, если СЗР принимает значение 1. АЦП повторяет этот алгоритм вплоть до последнего младшего бита (МЗР) (см. рис. 3). Таким образом, собственно аналого-цифровое преобразование происходит в течение числа тактов равного числу разрядов АЦП последовательного приближения. Следовательно, при прочих равных условиях время преобразования возрастает по мере увеличения разрядности АЦП. Именно по этой причине в МК со встроенными АЦП последовательного приближения можно выбирать режим преобразования с меньшим числом разрядов. Например, в 12-разрядном АЦП выбирается режим 8-разрядного преобразования; при этом возрастает погрешность дискретизации, но уменьшается время преобразования.

В качестве примера достижения максимальных результатов можно привести АЦП последовательного приближения AD4020BCPZ-RL7 компании Analog Devices. Производительность этого преобразователя достигает 1,8 Мвыб/с при 20-разрядном разрешении.

Если АЦП работает в многоканальном режиме, следует помнить, что его максимальная производительность АЦП может уменьшиться из-за увеличения времени перезаряда входного конденсатора С (см. рис. 1). Причем, это время зависит не только от АЦП, но и от постоянной времени внешнего пассивного RSCS-фильтра. Таким образом, при расчете следует учитывать худший вариант, когда конденсатор полностью перезаряжается при переключении от одного канала к другому. Команда на старт преобразования подается исходя именно из такого варианта. В противном случае погрешность преобразования может возрасти.

Рисунок 3

Рисунок 4

Рисунок 5

Временная диаграмма работы 4-бит АЦП последовательного приближения

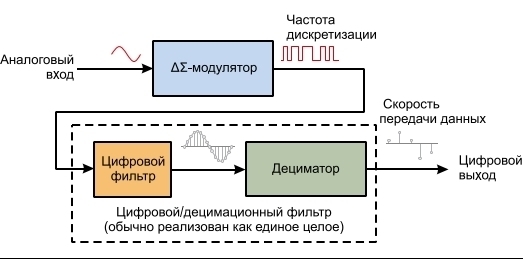

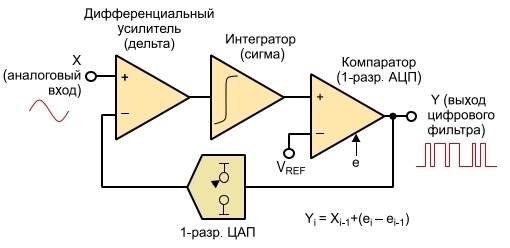

Структурная схема ΔΣ АЦП с базовой топологией

Входной каскад модулятора ΔΣ АЦП

Рисунок 6

Рисунок 7

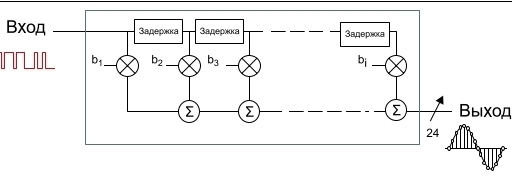

Усредняющий цифровой КИХ-фильтр

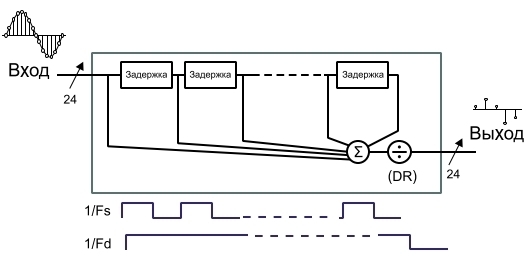

Децимация данных

Сигма-Дельта АЦП

Итак, в состав АЦП последовательного приближения входит несколько каскадов. При изготовлении невозможно обеспечить их полное согласование, особенно соотношение между емкостями. Сложно получить и малые значения емкостей для каскадов младших разрядов. Например, в 18-разрядном АЦП емкость каскада МЗР должна быть в 218 раз меньше, чем емкость конденсатора СЗР. По этим причинам АЦП последовательного приближения плохо подходят для прецизионных измерений сигналов микровольтового уровня, когда необходимо обеспечить минимальную абсолютную погрешность. В таких случаях прибегают к использованию ΔΣ АЦП. На сегодняшний день на рынке предлагается относительно большой выбор 24-разрядных ΔΣ АЦП.

Структурная схема ΔΣ АЦП показана на рисунке 4. В этой топологии ΔΣ АЦП имеет сигмадельта модулятор, последовательно соединенный с цифровым фильтром. Помимо этой базовой топологии, большинство ΔΣ АЦП имеет множество других компонентов. Однако все ΔΣ-преобразователи основаны на этой базовой схеме.

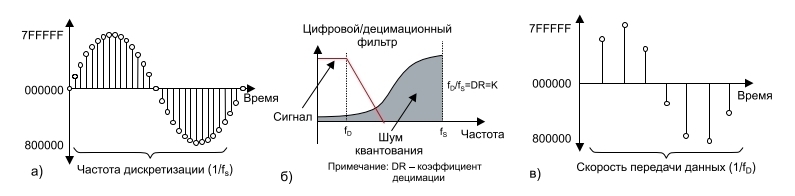

Показанный на рисунке 4 входной сигнал может быть и синусоидальным, и постоянным. В этой статье рассматривается только синусоидальный входной сигнал. ΔΣ-модулятор оцифровывает синусоидальную волну одного цикла в 1-разрядный поток с частотой дискретизации выходного сигнала ΔΣ-модулятора FS. Хотя преобразование 1-разрядного модулятора имеет высокий шум квантования, фактически шум сигнала «формируется» на более высоких частотах. Это открывает путь для преобразования с низким уровнем шума и высоким разрешением на выходе цифрового фильтра.

На выходе модулятора цифровой фильтр накапливает 1-разрядные результаты ΔΣ-модулятора и выполняет алгоритмы фильтрации. Выходной сигнал цифрового фильтра отражает аналоговый входной сигнал в цифровом виде, сохраняя при этом выходную частоту FS. Теперь сигнал находится исключительно в цифровой области. цифровой фильтр нижних частот, или децимационный фильтр, ослабляет высокочастотный шум и замедляет выходную скорость передачи данных 1/FD. цифровой/децимационный фильтр дискретизирует и фильтрует поток 1-разрядного кода модулятора до более медленного многоразрядного кода.

В то время как большинство преобразователей имеют только одну частоту дискретизации, ΔΣ-преобразователь имеет две: частоту дискретизации (FS) и выходную частоту данных (FD). Отношение этих двух частотных переменных определяет коэффициент децимации системы (DR) согласно уравнению (1): DR = FS/FD. (1)

ΔΣ-модулятор выполняет фактическое аналого-цифровое преобразование, генерируя поток 1-разрядных кодов. Этот процесс начинается в дифференциальном усилителе. Входной каскад модулятора ΔΣ АЦП показан на рисунке 5. Как видно из него, дифференциальный усилитель (дельта) передает аналоговый сигнал в интегратор (сигма). На выходе интегратора компаратор с очень высокой частотой дискретизации (1/FS) сравнивает напряжение на выходе интегратора с опорным (VREF). Кроме того, компаратор формирует 1-разрядный поток в 1-разрядном цифро-аналоговом преобразователе (ЦАП). Затем модулятор оценивает разницу между аналоговым входным сигналом и аналоговым выходом ЦАП, находящегося в цепи обратной связи.

Δ Σ- модулятор формирует шум на высоких частотах, что обусловлено работой интегратора и контура обратной связи ЦАП. Справа внизу на рисунке 5 представлено уравнение переноса (2): Yi = Xi-1 + (ei – ei–1). (2)

Модулятор оцифровывает входной сигнал (Xi) в 1-разрядный выходной код (Yi) с шумом квантования (ei). В частности, выход модулятора (Yi) равен входу (Xi–1) плюс шум квантования (ei – ei–1). По этой формуле шум квантования вычисляется как разница между текущей ошибкой (ei) и предыдущей ошибкой модулятора (ei–1).

фильтрация осуществляется с помощью усредняющих фильтров, называемых sinc-фильтрами, в которых используется линейно-фазовая конечная импульсная характеристика (КИХ). Она представляет собой цифровой фильтр нижних частот, структурная схема которого представлена на рисунке 6. Все коэффициенты (bx) фильтра в рассматриваемом случае равны 1.

Выходной поток битов модулятора является входом этого цифрового фильтра, а тактовая частота дискретизации модулятора определяет время задержки. С помощью этого алгоритма усреднения цифровой КИХ-фильтр генерирует 24-разрядное цифровое представление аналогового входного сигнала, обладающее низким уровнем шума, причем выборки происходят с частотой дискретизации модулятора. Затем фильтр децимации уменьшает выходную скорость передачи данных. Процесс децимации данных с коэффициентом DR показан на рисунке 7. На рисунке 8 представлен конечный результат преобразования исходного синусоидального сигнала.

Рисунок 8

Рисунок 9

Результат преобразования ΔΣ АЦП: а) исходный сигнал во временной области; б) спектр шума квантования на выходе модулятора; в) выходной сигнал дециматора во временной области

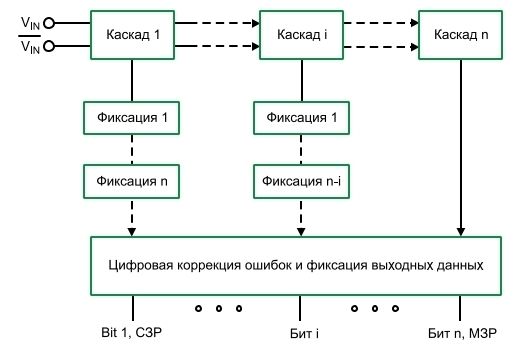

Структурная схема конвейерного АЦП

Рисунок 10

Связь между производительностью и разрядностью АЦП разных типов

Конвейерные АЦП

В приложениях с производительностью в сотни или да же тысячи Мвыб/с не обойтись без конвейерного АЦП. Его структурная схема приведена на рисунке 9. Конвейерный АЦП состоит из нескольких последовательных каскадов. В первом каскаде оценивается значение старшего бита (СЗР), затем сигнал обрабатывается и передается в следующий каскад для преобразования (СЗР – 1). Поскольку каждый каскад выполняет свою работу одновременно с другими, а не последовательно за предыдущим, производительность конвейерных АЦП весьма высока.

Показанные на рисунке 9 ступени аналогичны по функциям и преобразуют только один или два бита. В каждом каскаде выполняется выборка и удержание, имеется параллельный АЦП с низким разрешением и компоненты формирования сигнала. Первый каскад получает выборку и немедленно выдает значение СЗР. цифровое значение СЗР подается в первую схему фиксации (фиксация 1). Если значение СЗР равно единице, ступень вычитает значение заряда СЗР из выборки. Затем конвейерный преобразователь применяет к оставшемуся сигналу коэффициент усиления 2. После завершения операций ступень передает разность аналоговых сигналов последующим ступеням. Привлекательность конструкции с двукратным коэффициентом усиления заключается в том, что от ступени 1 до ступени n схема принципиально одинаковая.

Число каскадов часто совпадает с числом разрядов АЦП. Конечный результат преобразования является совокупностью результатов каждой ступени. Такой процесс преобразования приводит к задержке данных всего лишь на несколько тактов, причем их число всегда меньше числа каскадов. Примером достижения высоких результатов может служить 2-канальный АЦП конвейерного типа ADS54J20 компании Texas Instruments. При разрешении 12 бит его производительность достигает 1 Гвыб/с.

Рисунок 11

Рисунок 12

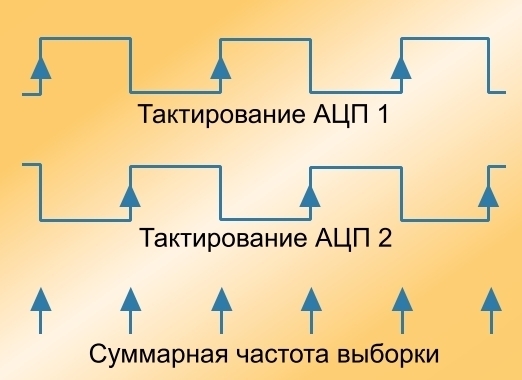

актирование двух параллельных АЦП

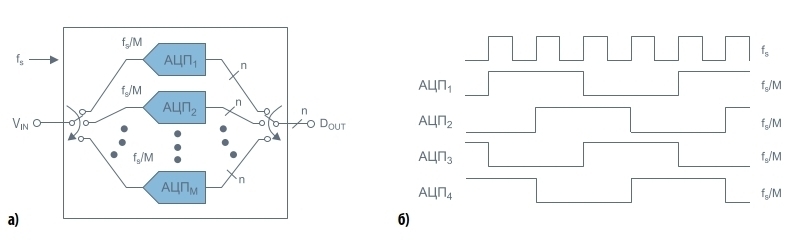

а) параллельное включение нескольких АЦП; б) временная диаграмма их работы

Рисунок 13

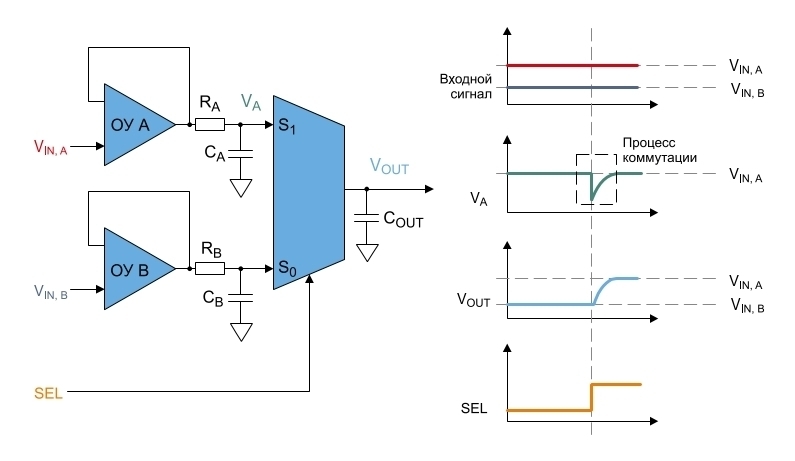

Процесс коммутации каналов в двухканальной системе

АЦП с чередованием

Связь между производительностью и разрядностью рассмотренных выше АЦП разных типов показана на рисунке 10. Как из него видно, производительность АЦП конвейерного типа может превысить 1 Гвыб/с при меньшей разрядности. Это внушительная цифра, однако в ряде приложений недостаточно даже такой производительности. В таких случаях используется решение, в котором несколько АЦП включены параллельно и тактируются одной и той же частотой, но их тактовые последовательности сдвинуты по фазе. Такой метод включения АЦП называется методом чередования (interleaving ADC).

На рисунке 11 показан простой случай использования двух параллельных АЦП. Их импульсные последовательности синхронизации сдвинуты друг относительно друга на 180°. Видно, что при этом суммарная частота выборки ношение сигнал/шум. При увеличении числа параллельно работающих АЦП эта проблема усугубится.

Во-вторых, паразитные выбросы с точно такими же последствиями могут появиться из-за несогласованности АЦП (напряжения смещения и его температурного дрейфа, коэффициента преобразования, погрешности и т. д.). В этом случае даже при преобразовании постоянного сигнала коды на выходе АЦП были бы разными, т. е. несогласованность АЦП приведет к появлению ложных составляющих в сигнале. Мы перечислили только две причины, но, надеемся, что убедили отдать предпочтение готовому решению, а не создавать свое. Только производитель может добиться высокой согласованности нескольких АЦП и трактов тактирования, разместив все компоненты на одном кристалле.

Рисунок 14

Рисунок 15

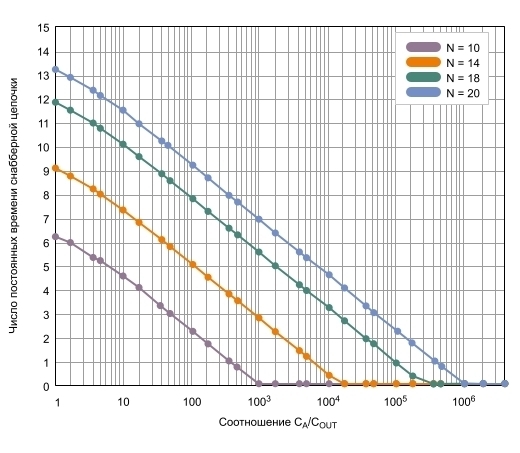

Зависимость времени установления tSET от соотношения CA/COUT при разном числе разрядов АЦП

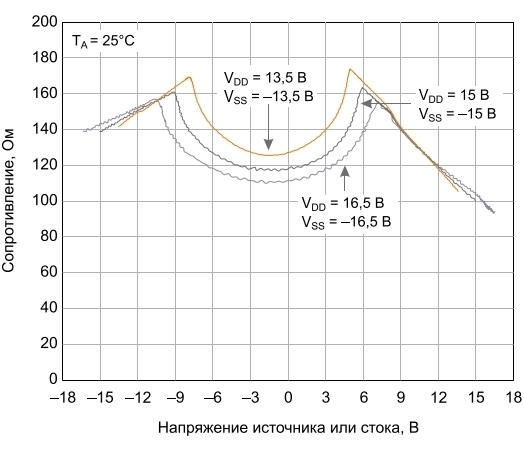

Изменение сопротивления открытого канала мультиплексора в зависимости от напряжения питания и коммутируемого напряжения

Рисунок 16

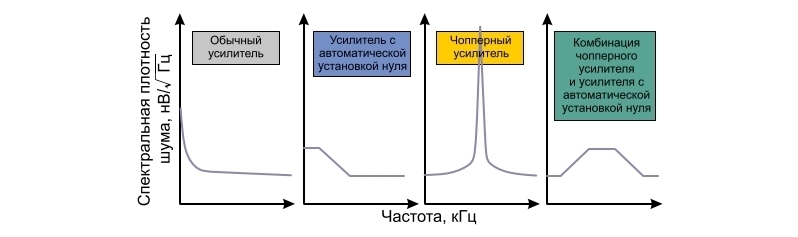

Сравнение графиков спектральной плотности шума усилителей

Некоторые источники погрешностей не связанные с АЦП

Погрешности АцП приводятся в доку- ментации изготовителя, но, к сожа- лению, ими не исчерпывается весь перечень погрешностей. Свою лепту вносят и погрешности измерительно- го тракта, которые можно разделить на динамические и статические. Очень кратко рассмотрим их.

Динамические погрешности чаще всего происходят из-за ошибки при выборке сигнала, особенно в много- канальной системе с мультиплексором входных каналов. Рисунок 13, на кото- ром показана коммутация каналов в двухканальной системе, иллюстрирует данный вывод. При подаче управляюще- го сигнала SEL мультиплексор отключает от АцП канал «А» с сигналом VIN, A и под- ключает канал «В» VIN, B. При этом, как видно из рисунка, за время выборки напряжение на конденсаторе COUT долж- но измениться с CB до CA.

Длительность перезарядки конден- сатора COUT зависит от постоянной вре- мени RACA снабберной цепочки. Этот процесс можно считать закончившимся, когда напряжение на этом конденсаторе отличается от установившегося значе- ния на величину менее 1 МЗР АцП.

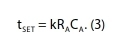

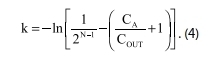

Необходимое для этого время tSET вычисляется из соотношения следую- щим образом [4]:

Величина k определяется из форму- лы (4):

Зависимость времени установления tSET от соотношения CA/COUT при разном числе разрядов АЦП показана на рисунке 14. В формулах (3) и (4) не учтено сопротивление открытого канала мультиплексора и изменение этого сопротивления в зависимости от напряжения питания и коммутируемого напряжения. Пример этих зависимостей приведен на рисунке 15. Статические погрешности складываются из напряжения смещения усилителей, температурного дрейфа напряжения смещения и шумов. Последнее весьма значимо при использовании АЦП с большим числом разрядов. Например, в 24-разрядном АЦП при полной входной шкале 5 В значение МЗР составит 298 НВ. Расчет шума – довольно трудоемкая задача, и в специальной литературе можно найти немало материалов на эту тему. Мы не будем пытаться их воспроизвести, но сошлемся на [5], где изложены основные положения, и на [6]. На наш взгляд, изложенный в этих источниках метод достаточно лаконичен, прост и вполне подходит для инженерных расчетов. В то же время значение МЗР 12-разрядного АЦП при 5-В входной шкале составляет 1,22 мВ, и шумами в данном случае вполне можно пренебречь. Для уменьшения статической погрешности применяются либо операционные прецизионные усилители, либо специализированные операционные усилители, позволяющие свести смещение практически к нулю. Последние более предпочтительны, когда речь идет о крайне малых смещениях и шумах. В этих усилителях используются три топологии: - чоппер; - автоматическая установка нулевого смещения; - комбинация обоих методов. В чопперном усилителе применяется метод модуляции–демодуляции. Смещение при этом является крайне малым, как и шумы в низкочастотной области, где выделяется шум вида 1/f, но зато очень велик шум и помехи на частоте модуляции. Если полоса пропускания сигнала значительно ниже частоты модуляции, этот недостаток легко устраняется с помощью последующей фильтрации. В усилителе с автоматической установкой нуля используются два усилителя. В одном из них (вспомогательном с закороченными выводами) в первой части рабочего цикла запоминаются смещение и шум 1/f, а во втором цикле это смещение вычитается из выходного сигнала основного усилителя. Производители не всегда указывают, по какой топологии выполнен операционный усилитель, но с изрядной долей уверенности можно утверждать, что при смещении менее 5 мкВ речь идет об усилителе с одной из трех описанных топологий. На рисунке 16 схематично сравниваются графики спектральной плотности шума разных усилителей. Спектральная плотность шума специализированных усилителей не превышает нескольких десятков НВ/√Гц. При полосе пропускания 100 Гц среднеквадратичная величина шума составляет несколько сотен НВ. Для уменьшения суммарного шума и смещения малошумящие усилители с небольшим смещением следует установить в самом начале измерительного тракта и задать им максимально возможный коэффициент усиления.

Корзина пуста

0

шт.

/

$0

Оформить

Очистить