- 8 (812) 612-97-27

- СПБ, Курчатова дом 1А помещение 1Н

- order@das-elektro.de

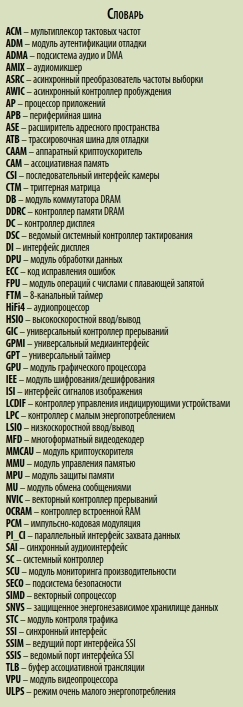

МИКРОКОНТРОЛЛЕРЫ СЕРИИ I.MX8 КОМПАНИИ NXP

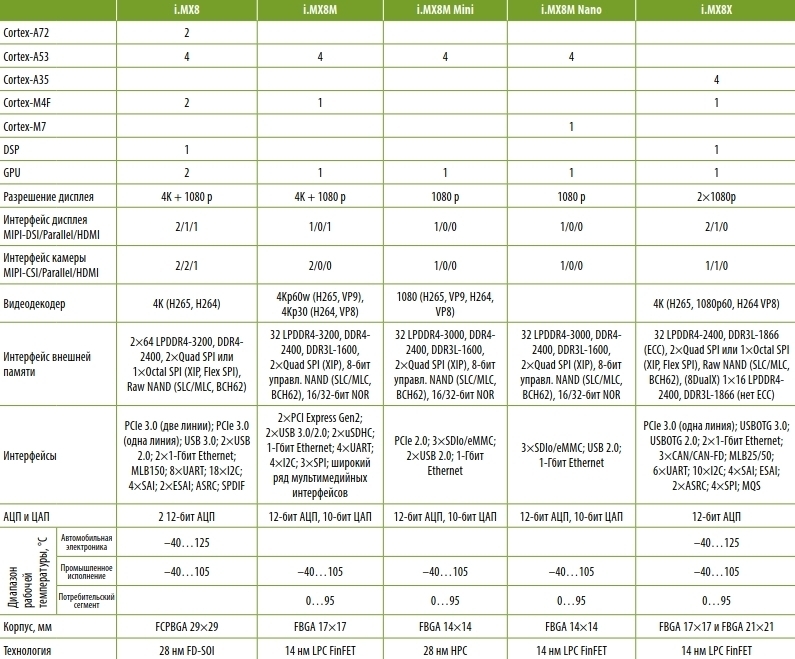

В статье рассматриваются некоторые основные, на взгляд автора, узлы новейших микроконтроллеров i.MX8X серии i.MX8. В начале статьи в табличном виде перечислены некоторые наиболее важные параметры микроконтроллеров семейств i.MX8 М и i.MX8X.

Введение

Микроконтроллеры (МК) приложений серии i.Mx8 представляют собой высокопроизводительную масштабируемую многоядерную платформу, в состав которой входят 1-, 2- и 4-ядерные кластеры ARM cortex. Они могут найти применение в критически важных приложениях, в мультимедиа и обработке графики, системах технического зрения, в промышленных приложениях. Ядро cortex-M4F встроено во все модификации МК и позволяет в реальном режиме времени выполнять критически важные задачи.

Некоторые основные параметры семейств МК i.Mx8, i.Mx8M и i.Mx8x приведены в таблице 1. Заметим, что статья написана «с пылу с жару» – серия продолжает развиваться, поэтому таблица 1 со временем может корректироваться. Все МК работают с широким рядом операционных систем: Android, Linux, Qnx, Green Hills, DornerWorks xEn, FreeRToS и с некоторыми операционными системами партнеров.

Ниже мы более–менее подробно, насколько это позволяют рамки журнальной статьи, рассмотрим МК семейства i.Mx8x, в котором, пожалуй, наиболее широко в настоящий момент представлены возможности серии. Возможности МК i.Mx8 мы постараемся описать в ближайшее время в отдельной статье.

Процессорные ядра

В семействе МК i.Mx8 используются разные процессорные ядра, а именно: cortex-M4F; cortex-M7; cortex-A35; cortex-A53 и cortex-A72. Ядра cortex-M4F и cortex-M7 имеют хорошо известную 32-бит архитектуру Armv7-M; МК с этими ядрами подробно рассматривались, и мы не будем их описывать. Но несколько слов следует сказать о ядрах cortex-A35; cortex-A 53 и cortex-A72 – с ними выпускаются не так уж много МК

В состав ЦП может входить не только одно-единственное ядро, но и кластер, объединяющий до четырех ядер. В таблице 1 для каждого МК указано именно число ядер в процессорном кластере, а нечисло процессоров. Некоторые основные параметры описываемых ядер приведены в таблице 2. Все эти ядра имеют 64-бит архитектуру Armv8 -A , век торный сопроцессор neon, модуль работы с числами с плавающей точкой, технологию защиты TrustZone и 40-бит физическую адресацию.

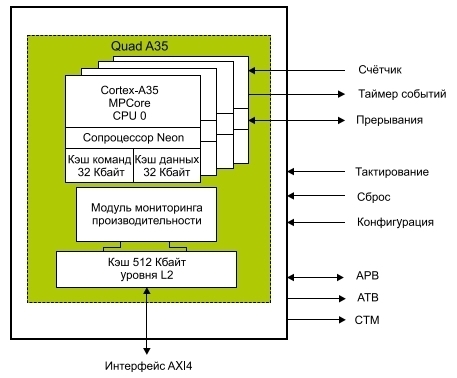

cortex-A35 и cor tex-A 53 представляют собой ядра средней производительности с малым энергопотреблением. Ядро cortex-A72 имеет высокую производительность. На рисунке 1 схематично, «с точки зрения микроконтроллера», показана структурная схема ЦП, состоящего из 4-ядерного кластера cortex-A35 МК семейства i.Mx8x. Идентичную структурную схему имеет 4-ядерный кластера cortex-A53 МК семейства i.Mx8M; имеется лишь одно отличие – объем кэша памяти уровня L2 составляет 1 Мбайт.

Триггерная матрица cTM объединяет сигналы отдельных ядер в один канал и позволяет МК работать с 4-ядерным кластером как с одним ЦП. Связь с МК осуществляется через периферийную шину APB.

Рисунок 1

Структурная схема ЦП, состоящего из 4-ядерного кластера Cortex-A35

Таблица 1

Некоторые параметры микроконтроллеров семейства i.MX8

Таблица 2

Некоторые основные параметры процессорных ядер Cortex-A35, Cortex-A 53 и Cortex-A72

Архитектура MK I.MX8X

Некоторые основные параметры процессорных ядер Cortex-A35, Cortex-A 53 и Cortex-A72 входят модификации i.Mx8 xQuadxPlus и i.Mx8 DualxPlus. ЦП первого из них состоит из 4 - ядерного кластера cortex-A35, а второго – из 2-ядерного кластера cortex-A35. Вычислительные возможности МК увеличивает процессор DSP компании Tensilica, который предназначен для аудио- и видеокодеков, а также для предварительной и последующей обработки данных, благодаря которому высвобождаются ресурсы ЦП.

Структурная схема МК представлена на рисунке 2. Кратко перечислим основные особенности ЦП cortex-A35:

– 32-Кбайт кэш команд уровня L1 для каждого ядра с защитой по четности;

– 32-Кбайт кэш данных уровня L1 для каждого ядра с кодом исправления ошибок (Ecc);

– 512-Кбайт кэш уровня L2 для всех ядер с кодом Ecc;

– сопроцессор SiMD и блок для работы с плавающими числами;

– криптоускорители.

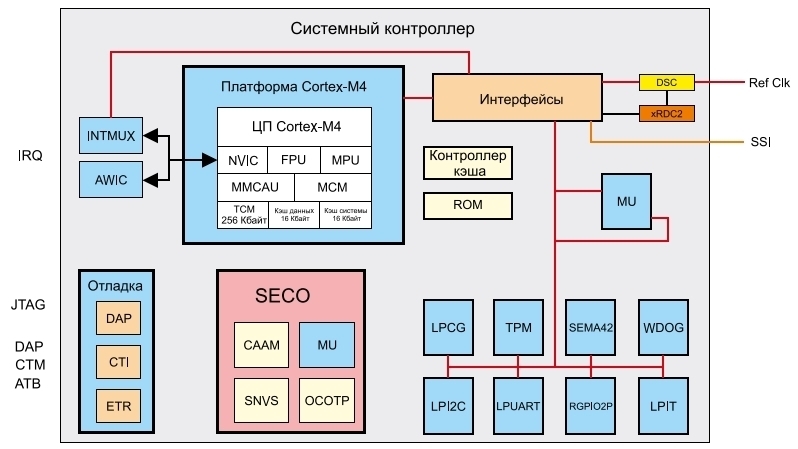

Упомянем и основные особенности ядра cortex-M4F:

– 16 -Кбайт кэш команд с защитой по четности;

– 16-Кбайт системный кэш с защитой по четности;

– 256-Кбайт тесно связанная память;

– модуль FPU операций с числами с плавающей запятой;

– модуль защиты памяти MPU;

– модуль криптоускорителя MMcAU.

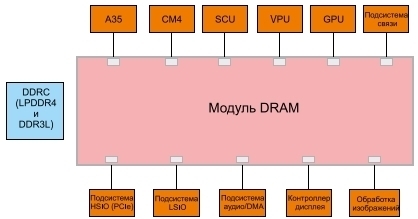

Отметим еще системный контроллер Sc, который управляет большей частью ресурсов МК и базируется на ядре cortex-M4. Некоторые другие ресурсы МК мы рассмотрим в других разделах. Упрощенная структурная схема МК показана на рисунке 3. Модуль DB является коммутатором, обеспечивающим подключение подсистем МК к внешней памяти DRAM по схеме «точка–точка» через синхронный интерфейс SSi. Модуль непосредственно подключен к контроллеру памяти МК. На рисунке 4 показано, как организована цепочка связи между подсистемой МК и внешней памятью DRAM.

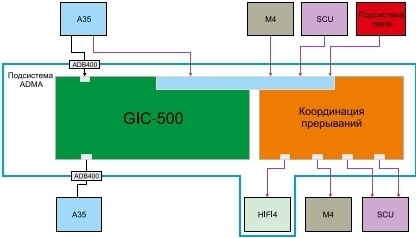

Для обслуживания прерываний в МК используется универсальный контроллер прерываний Gic компании ARM и модуль координаций прерываний, работающий в асинхронном режиме. Контроллер Gic связан только с процессорным кластером cortex-A35, а модуль координации прерываний осуществляет маршрутизацию прерываний между cortex-A35, cortex-M4F и системным контроллером Sc. Структурная схема их взаимодействия показана на рисунке 5.

В качестве источника тактовой частоты МК i.Mx8x использует два внешних осциллятора с частотой 32 кГц и 24 МГц и нестабилизированный встроенный осциллятор 200 МГц. Каждая подсистема имеет свою достаточно разветвленную схему тактирования. Внешний 24-МГц осциллятор служит источником главной частоты для всех подсистем.

Безопасность МК обеспечивает подсистема безопасности SEco. В ее состав входят следующие модули:

– ADM – модуль аутентификации отладки;

– cAAM – аппаратный криптоускоритель, который реализует хэш-функцию и генератор случайных чисел RnG;

– защищенная 64-Кбайт SRAM с контролем доступа и стиранием ключей;

– iEE – модуль шифрования/дешифрования, который производит кодирование и декодирование данных «на лету»;

– контроллер безопасности на ядре cortex-М0+;

– SnVS – защищенное энергонезависимое хранилище данных;

– oTP – хранение ключей;

– MU – модуль сообщений. Четыре модуля MU позволяют подсистеме безопасности обмениваться сообщениями с системным контроллером и с cortex-M4F, cortex-M7.

Рисунок 3

Рисунок 4

Упрощенная структурная схема МК

Цепочка связи между подсистемой МК и внешней памятью DRAM

Рисунок 5

Структурная схема организации прерываний в МК

Рисунок 6

Структурная схема верхнего иерархического уровня контроллера SC

Системный контроллер SC

Отметим интересную особенность архитектуры МК. Процессорные подсистемы cortex-A35 и cortex- M4F неимеют прямого доступа к ресурсам МК – им доступны эти ресурсы только через системный контроллер Sc. Такая организация позволяет лучше изолировать процессорные подсистемы и освободить их от рутинных операций. Коммуникация между процессорными подсистемами и системным контроллером Sc осуществляется через модули обмена сообщениями MU.

Системный контроллер обеспечивает:

- загрузку и инициализацию;

- коммуникации;

- управление питанием;

- управление ресурсами;

- конфигурацию внешних выводов;

- управление таймерами;

- управление прерываниями;

- некоторые дополнительные сервисы.

Структурная схема верхнего иерархического уровня контроллера Sc показана на рисунке 6. Заметим, что процессорное ядро cortex-M4F, входящее в состав контроллера Sc, используется только контроллером и не доступно пользователю. Внутренние прерывания обслуживаются контроллером, но до восьми локальных прерываний могут быть направлены для обслуживания другими ресурсами.

За счет управления внутренними шинами контроллер поддерживает одновременную работу нескольких сред. Для пробуждения системы используется асинхронный контроллер пробуждения AWic. Контроллер с низким энергопотреблением LPc реализует выход контроллера Sc из режима глубокого сна.

Управление питанием, тактированием и сбросом также осуществляется системным контроллером, как и управление ресурсами МК. В последнем случае контроллер Sc распределяет периферийные устройства и области памяти между несколькими выполняемыми задачами.

Память

Интерфейс внешней памяти DRAM состоит из модуля DB, который реализует непосредственное подключение к интерфейсу DRAM через несколько портов МК. Ширина шины на стороне PHY составляет 32 бит, частота тактирования шины – 1200 МГц. Интерфейс обеспечивает арбитраж для всех подсистем и периферийных модулей.

В состав подсистемы памяти входит монитор производительности памяти, который подсчитывает число обращений со стороны интерфейса Axi и контроллера DDRc памяти DRAM, а также отслеживает число считываний из памяти LPDDR3/LPDDR4. В состав монитора входит несколько счетчиков; один из них отсчитывает число циклов, другие считают количество служебных сигналов. При переполнении счетчиков формируется прерывание.

Контроллер памяти DDRc вносит минимальную задержку и имеет низкое энергопотребление. Он поддерживает память DDR3-L и LP-DDR4 и преобразует транзакции системной шины в команды протокола интерфейса DFi, соответствующего протоколу DDR. Кратко перечислим некоторые функциональные возможности контроллера:

- динамическое планирование запросов, позволяющее уменьшить задержку и увеличить производительность памяти;

- чтение и запись буферов ассоциативной памяти;

- задержка записи для оптимизации производительности шины данных DRAM;

- выполнение команд вне очереди;

- поддержка трех типов чтения: с высоким приоритетом;

с переменным приоритетом;

с низким при- оритетом;

- поддержка двух типов записи: с обычным приоритетом;

с переменным приоритетом;

- включение режима пониженного энергопотребления DRAM при отсутствии транзакций.

Помимо интерфейса для DRAM предусмотрены интерфейсы: - Quad SPi для связи с ПЛИС;

- 2×Quad SPi или 1×octal SPi (FlexSPi) для подключения загрузочной флэш-памяти SPi noR;

- 2×SD 3.0; - eMMc5.1/SD3.0; - RAW nAnD.

Рисунок 7

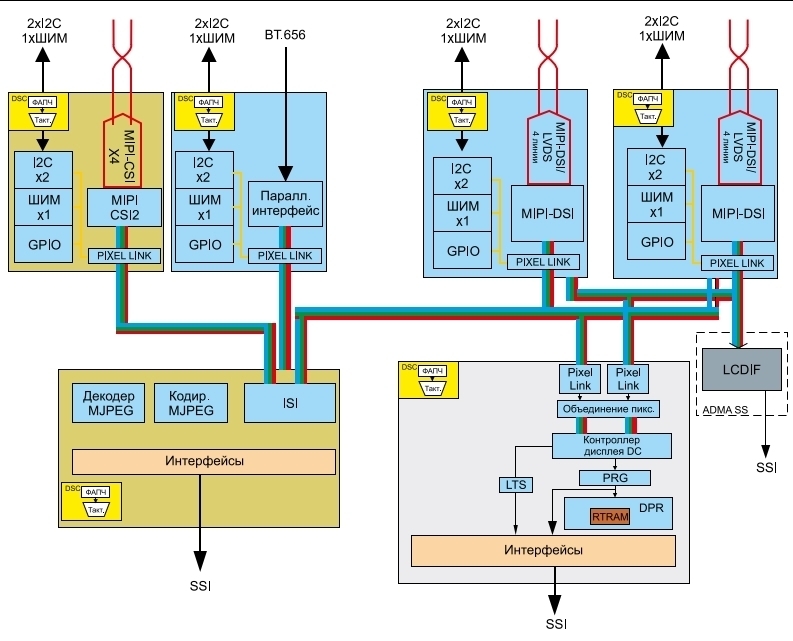

Рисунок 8

Коммуникации между подсистемами дисплея, камеры и обработки изображения

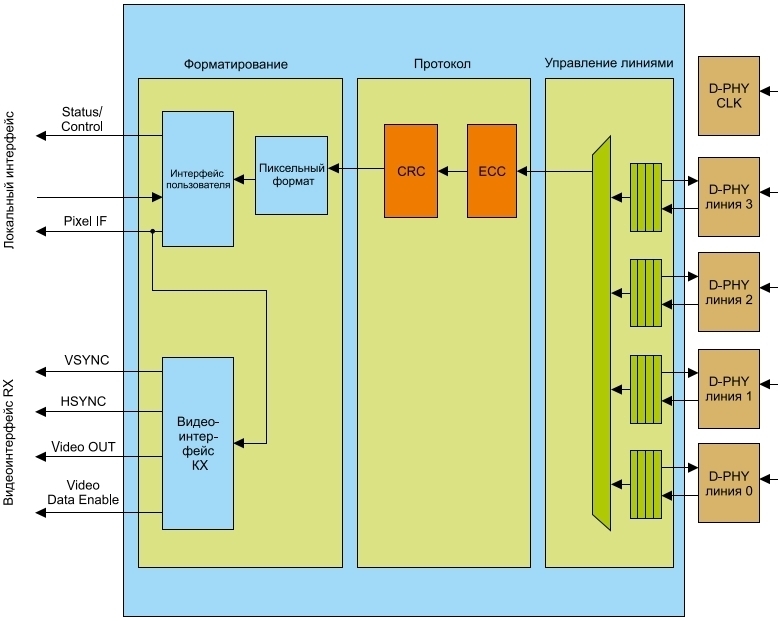

Структурная схема подсистемы MIPI CSI

Рисунок 9

Структурная схема аудиоподсистемы ADMA

Подсистемы диспле, камеры и обработки изображения

Эти подсистемы связывает шины передачи pixel link1. Связь между подсистемами показана на рисунке 7. Один из выходных каналов контроллера дисплея может быть скопирован в интерфейс сигналов изображений iSi, в котором происходит предварительная обработка пиксельных данных, после чего эти данные сохраняются в памяти. Модуль iSi может обрабатывать пиксельные данные из трех источников.

Для обработки данных используется до восьми каналов. Один и тот же поток данных может быть направлен одновременно в разные каналы, например, если требуется получить полноразмерную и уменьшенную версии изображения. В канале обработки производится масштабирование сигнала, преобразование цветовых форматов, удаление гребенки (de-interlacing) и формирование выходного буфера. После предобработки модуль iSi пересылает данные в память.

Контроллер дисплея Dc полностью поддерживает два ЖКД; чтение контента осуществляется из буфера памяти. Контроллер представляет собой 3-канальный блок обработки изображений, который выполняет операции масштабирования, слияния, поворота и деформирования изображения. В его состав входит модуль передачи фрагмента растрового изображения (Blit engine), который позволяет выполнять преобразования из памяти в память.

Встроенный механизм секвенсора команд выполняет последовательность команд, извлекаемых контроллером из памяти, без помощи ЦП. Обработанные изображения передаются через два интерфейса – MiPi-DSi/LVDS.

Последовательный интерфейс камеры cSi камеры может передавать до четырех потоков данных и преобразовывать их во внутренний пиксельный формат МК для MiPi-DSi/LVDS. Параллельный интерфейс камеры также преобразует входные сигналы камеры во внутренний пиксельный формат МК.

Подсистема обработки изображений состоит из интерфейса сигналов изображения iSi, энкодера MJPEG и декодера MJPEG. Она может получать данные из трех источников (MiPi cSi, Dc0, параллельный интерфейс) и записывать их в память. Подсистема способна в реальном времени кодировать и декодировать потоки JPEG. Кодер и декодер работают независимо друг от друга; максимальная производительность каждого из них составляет 400 Мпикс. Поддерживаются форматы YUV444, YUV422, YUV420, RGB. Четыре контекста выполняют разные наборы команд независимо друг от друга.

В состав подсистемы параллельного захвата данных входит параллельный интерфейс BT 656 и связанные с ним периферийные модули. Эта подсистема коммутируется с параллельным интерфейсом камеры. Поддерживаются форматы RGB, RAW и YUV 422. Модуль ШИМ используется для тактирования интерфейса камеры.

Подсистема MiPi cSi обрабатывает все входные данные устройств отображения

– камер и датчиков. Контроллер подсистемы реализует все три уровня интерфейса

– пикселы, нижний уровень и управление линиями данных, 1–4 линии. Скорость передачи данных по каждой линии варьируется в пределах 80 Мбит/с…1 Гбит/с; в этом случае обеспечивается изображение с размерностью 4K при 30 кадрах/с.

В режиме низкого энергопотребления скорость передачи данных снижается до 10 Мбит/с. Кроме того, поддерживается режим очень малого энергопотребления ULPS. Подсистема имеет важное значение, поэтому ее описание дополнит структурная схема (см. рис. 8). На ней достаточно подробно показаны все связи подсистемы. Через локальный интерфейс пользователь получает пакеты от интерфейса MiPi.

Подсистема MiPi-DSi/LVDS – часть дисплейного интерфейса Di, которую можно подключить к контроллеру дисплея через шины pixel link. Эта подсистема может быть связана с MiPi-DSi или дисплейным интерфейсом LVDS. Она поддерживает до четырех линий интерфейса DSi и дисплеи, начиная с QQVGA с разрешением 160×120 пикс. и заканчивая WUxGA с разрешением 1920×1200 пикс., с глубиной цветности 24 бит и 60 кадрами/с.

Подсистема интерфейса iSi через шины pixel link может взаимодействовать с пятью источниками сигналов. В ней происходит конвейерная обработка данных; каждый конвейер обрабатывает одну строку изображения. Поддерживается размерность 4K при 30 кадрах/с и глубине цветности 24 бит.

Параллельный интерфейс захвата данных Pi_ci подключается к параллельным интерфейсам камеры. Максимальная частота тактового сигнала составляет 150 МГц. Входные данные могут иметь следующие форматы:

– 8/10-бит интерфейс cSi;

– 8/24-бит RGB, Ycbcr, YUV;

– 8/12/10/16-бит данные фильтров Байера.

Контроллер дисплея являетcя основным модулем, управляющим дисплеями. Он может управлять тремя независимыми ЖКД через два интерфейса MiPi или LVDS и через один параллельный интерфейс. В изображении комбинируются до 18 слоев. Контроллер имеет высокую устойчивость к отказам даже в случае сбоя программного обеспечения. В состав каждого из двух PHY-интерфейсов MiPi-DSi/LVDS входят четыре линии MiPi-DSi и четыре линии LVDS. Интерфейсы могут быть объединены в единый двухканальный интерфейс LVDS. Параллельный 24-бит интерфейс имеет пропускную способность 720p60, но пропускная способность памяти DDR может ограничивать разрешение.

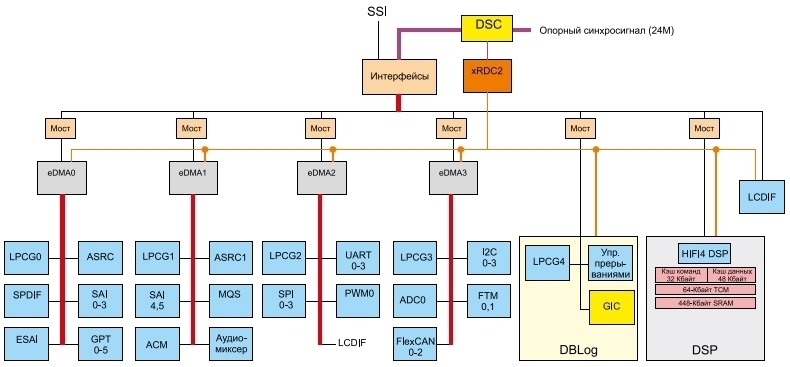

Подсистема ADMA аудио и DMA

В состав подсистемы ADMA входят аудиоустройства и некоторые системные модули. Структурная схема ADMA приведена на рисунке 9. Рисунок лучше всяких слов расскажет о построении ADMA, в которой нет уникальных устройств, поэтому мы в этом разделе ограничимся перечислением основных модулей и их очень кратким описанием. Мы сделаем лишь небольшое исключение для аудиопроцессора HiFi4. Главные функции ADMA:

- управление аудиопериферией, DSP и некоторыми модулями обработки данных;

- использование усовершенствованного модуля eDMA 3-го поколения для пересылки данных между медленной периферией и памятью. В общей сложности используются четыре контроллера eDMA, каждый из которых связан со своим набором периферийных модулей;

- управление универсальным контроллером прерываний Gic.

Мультиплексор тактовых частот AcM распределяет тактовую частоту в подсистеме ADMA. Аудиомикшер AMix смешивает два аудиопотока, каждый из которых состоит из восьми каналов, подключенных к выделенным портам синхронного аудиоинтерфейса SAi. Асинхронный преобразователь частоты выборки ASRc осуществляет импульсно-кодовую модуляцию (PcM). Усовершенствованные синхронный аудиоинтерфейс представляет собой многоканальный дуплексный последовательный порт для связи с аудиоустройствами. 8-канальный таймер FTM поддерживает операции захвата входного сигнала, сравнение выходного сигнала и генерацию ШИМ. Контроллер LcDiF управляет широким рядом индицирующих устройств. Цифровой интерфейс Sony/Philips SPDiF поддерживает прием и передачу данных в стандарте iEc60958. Универсальный таймер GPT используется для восстановления частоты тактирования.

Аудиопроцессор HiFi4, разработанный компанией Tensilica, является SiMD-процессором и служит для предварительной и окончательно обработки аудиосигналов. В состав процессора входят три основных компонента: модуль DSP, модуль для работы с числами с плавающей запятой и модуль для доступа, кодирования и декодирования потока переменной длины (код Хаффмана). Процессор HiFi4 может одновременно осуществлять операции с двумя 32-бит или четырьмя 16-бит переменными. Например, за одну операцию сложения выполняются два 32-бит сложения одновременно.

Умножители процессора осуществляют умножение четырех 32-бит операндов. Специальные скалярные операции типа 32×16 и 16×16 позволяют реализовать до восьми умножений за один цикл. 16-бит операции требуются для поддержки модели iTU-T/ETSi. Операции 32×16 и 32-бит операции могут осуществляться с целыми числами и с числами с фиксированной запятой. В HiFi4 исполняются VLiW-команды, что позволяет производить четыре операции одновременно.

Рисунок 10

Рисунок 11

Структурная схема процессора GPU

Упрощенная структурная схема подсистемы VPU

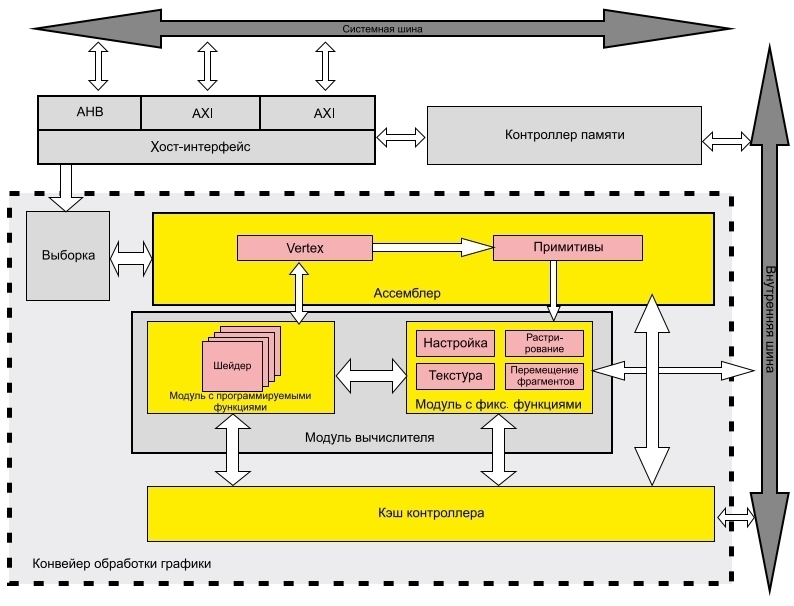

Графический процессор GPU

В состав процессора входят 16 шейдерных ядер Vec1 и четыре шейдерных ядра Vec4. Процессор поддерживает 2D-, 3D- и векторную графику, а также открытые стандарты в нескольких операционных системах. Перечислим основные графические APi:

– openGL ES 3.1/3.0;

– openGL ES 2.0/1.1;

– EGL 1.4;

– Directx 11 (9_3);

– openGL 3.1/3.0;

– openGL 2.1/2.0;

– openVG 1.1;

– opencL 1.2 FP/1.1 FP w/Global memory.

Структурная схема процессора приведена на рисунке 10. Через интерфейс хоста и шины Axi или AHB процессор подключается к внешней памяти и к служебным сигналам. Контроллер памяти управляет внутренней памятью процессора. Модуль выборки Fetch Engine встраивает высокоуровневые примитивы и команды в графический конвейер, где происходит их сборка для дальнейшей обработки.

Модуль с фиксированными функциями обработки преобразует треугольники и линии в пикселы, определяет координаты текстуры (максимальный размер текстуры составляет 8k×8k), осуществляет графическое усечение. Этот же модуль производит фильтрацию и интерполяцию графических данных. Блок текстуры обрабатывает два пиксела за 1 цикл. Модуль с программируемыми функциями является SiMD-вычислителем – он выполняет функции вершинного шейдера.

Заметим, что процессор GPU программируется через драйверы nxP. Компания не поддерживает программное обеспечение, с помощью которого программируются регистры GPU. APi-интерфейсы GPU представлены в отдельной документации.

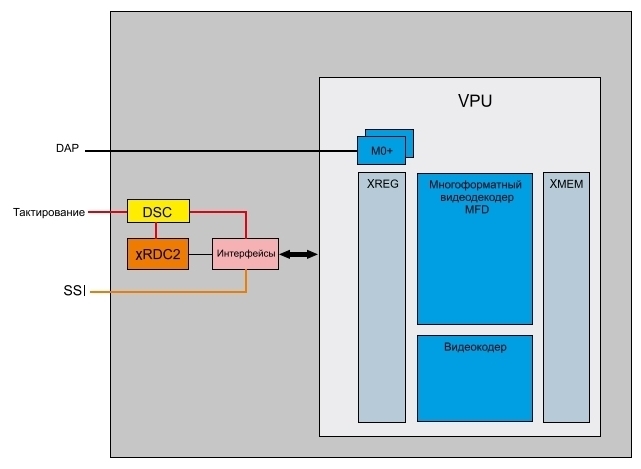

Видеопроцессор VPU

Упрощенная структурная схема подсистемы приведена на рисунке 11. VPU базируется на многоформатном аппаратном видеодекодере MFD, в состав которого входят два ядра cortex-М0+ с 16-Кбайт флэш-памятью, и видеоэнкодере. Регистры xMEM служат для обмена данными с памятью DDR, а xREG обеспечивают доступ со стороны регистров МК. Видеодекодер поддерживает следующие форматы:

– H.265 HEVc 4Kp30 Level 5.0;

– H.264 AVc;

– H.264 MVc;

– WMV9/Vc-1;

– MPEG 1 и 2;

– AVS Jizhun Profile (JP);

– MJPEG4.2 ASP, H.263;

– Divx 3.11;

– on2/Google VP6/VP8;

– RealVideo 8/9/10;

– JPEG и MJPEG A/B Baseline

Корзина пуста

0

шт.

/

$0

Оформить

Очистить