- 8 (812) 612-97-27

- СПБ, Курчатова дом 1А помещение 1Н

- order@das-elektro.de

В статье рассматриваются микроконтроллеры семейства RZ/N компании Renesas. Описание их основных модулей позволяет составить представление о возможностях микроконтроллеров этого семейства, предназначенного для решения широкого ряда задач промышленной автоматизации.

Введение

Прежде чем приступить к рассмотрению микроконтроллеров (МК) семейства RZ/N компании Renesas, буквально в двух словах опишем МК этой группы, чтобы указать в ней место МК RZ/N. В состав группы входят четыре семейства:

– RZ/A;

– RZ/G;

– RZ/N;

– RZ/T.

Наше описание семейств построено по принципу «от простого – к сложному». МК RZ/T базируется на процессорных ядрах Arm Cortex-R7. Они предназначены для высокопроизводительных МК, работающих в режиме реального времени. Их тактовую частоту можно увеличить до 600 МГц. Максимальная частота МК RZ/T – 600 МГц, что является предельным значением для Cortex-R7.

В МК RZ/T, как и в других микроконтроллерах семейства RZ, используется технология R-IN, основу которой составляет аппаратный ускоритель Ethernet, позволяющий ускорить процесс обработки в четыре раза. МК этой группы рекомендуется использовать в промышленных приложениях для управления электроприводами и исполнительными механизмами.

В состав семейства RZ/A входят многоядерные МК с процессорными ядрами Cortex-А9, тактируемые частотой 400 МГц и 528 МГц в последней модификации RZ/A2 М [1]. ядра Cortex-А9 предназначены для работы с достаточно сложными операционными системами, например Linux или Android. Микроконтроллеры RZ/A удобно использовать в коммуникационных и мультимедийных приложениях, а также для построения человеко-машинного интерфейса.

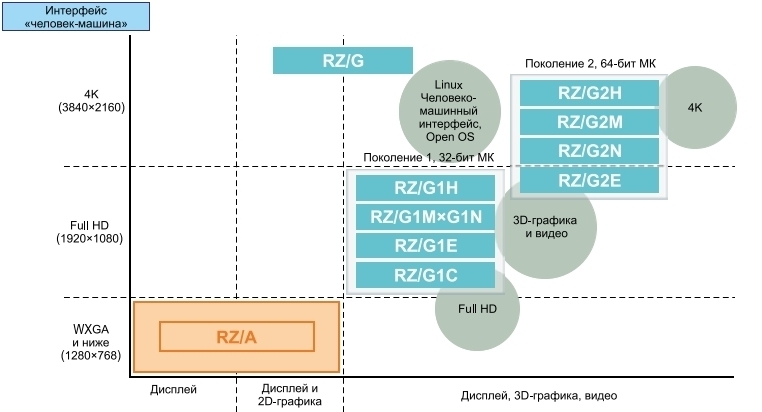

Семейство RZ/G делится на два подсемейства многоядерных МК – RZ/G1 и RZ/G2. Первое из них базируется на ядрах Cortex-А15 и Cortex-А7 с тактовой частотой до 1,5 ГГц, а второе – на 64-бит Cortex-А57 и Cortex-А53 с той же тактовой частотой. Причем, в самом мощном МК – по четыре ядра Cortex-А57 и Cortex-А53. Мы с удовольствием рассказали бы об этих МК, но, увы, документацию от компании можно получить только при условии подписания соглашения о неразглашении.

Рисунок 1

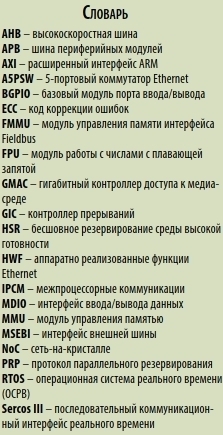

Словарь

Сравнительные возможности семейств RZ/G и RZ/A для создания интерфейса «человек-машина»

МК RZ/G предназначены для приложений с высокой вычислительной мощностью. Сопоставить семейства RZ/G и RZ/A поможет рисунок 1, на котором показаны возможности этих устройств для создания человеко-машинного интерфейса.

Многоядерные МК семейства RZ/N, наверное, можно позиционировать как переходный мостик от семейства RZ/T к семейству RZ/G – их можно использовать для управления в промышленных системах, но они обладают и очень неплохими сетевыми возможностями. МК базируются на ядрах Cortex-А7 и Cortex-М3. ядро Cortex-М3 было анонсировано в далеком 2004 г. Поскольку оно хорошо описано, мы не будем его описывать еще раз.

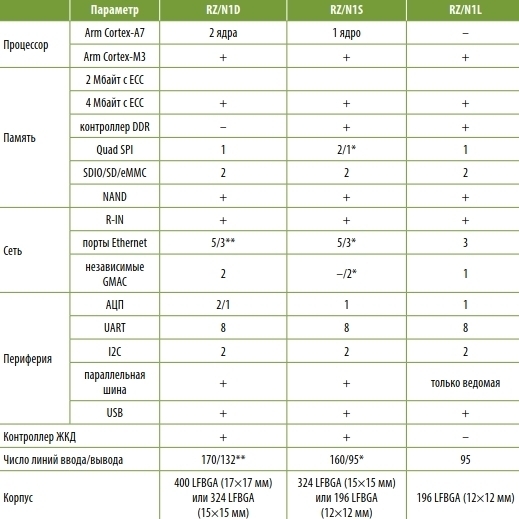

ядро Cortex-А7 появилось в 2011 г. Оно разработано для экономичных приложений и заменило ядро Cortex-А8, превзойдя его в производительности и энергоэффективности. К тому же, у ядра Cortex-А7 – меньше размеры. Распределение задач между ядрами в МК RZ/N иллюстрирует рисунок 2.

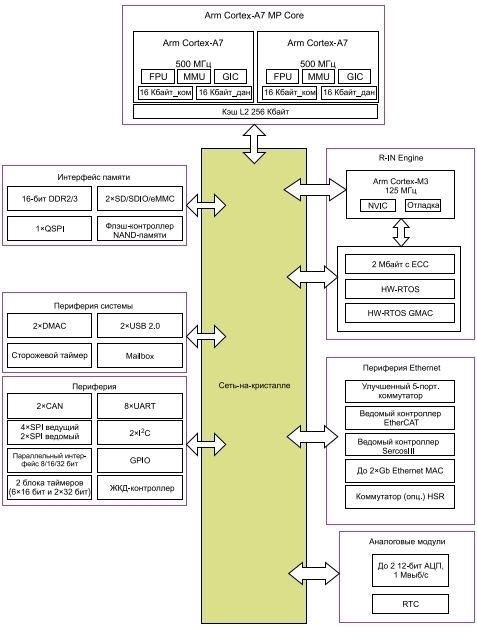

Далее мы опишем МКRZ / N1D на основе двуядерного кластера Cortex-А7 и ядра Cortex-М3. Этот микроконтроллер имеет наибольшие функциональные возможности среди других МК семейства. Некоторые основные параметры данных МК и их различия приведены в таблице. Структурная схема МКRZ/N1D показана на рисунке 3.

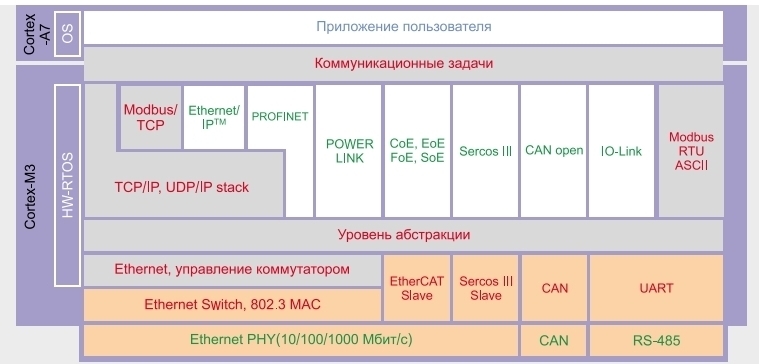

Таблица

Некоторые основные параметры МК семейства RZ/N1D и их различия

Рисунок 2

Рисунок 3

Распределение задач между ядрами МК семейства RZ/N

Структурная схема МК RZ/N1D

Функциональные модули MK RZ/N1D

Процессорные ядра и память

Поскольку процессорные ядра Cortex-А7 и Cortex-М3 хорошо известны, мы лишь кратко напомним читателям их основные параметры. В состав МК RZ/N1D входит двуядерный кластер Cortex-А7. Каждое ядро кластера содержит кэш команд уровня L1 емкостью 16 Кбайт и точно такой же по объему кэш данных. Общий для двух ядер кэш уровня L2 имеет емкость 256 Кбайт.

В состав каждого из ядер входит модуль работы с плавающими числами (FPU) и модуль управления памяти (MMU), а также контроллер прерываний (GIC). Максимальная частота тактирования ядер достигает 500 МГц. Заметим, что частота тактирования ядер должна быть кратна частоте тактирования сети NoC с коэффициентом кратности 1, 2 или 4. О процессорном ядре Cortex- М3 мы ничего нового не скажем. Заметим только, что его частота тактирования может меняться в пределах 15,625–125 МГц.

Межпроцессорные коммуникации между ядрами Cortex-A7 и Cortex-M3 осуществляются посредством трех почтовых ящиков. Модуль IPCM имеет три выхода прерываний, подключенных к каждому из трех ядер. В состав каждого почтового ящика входят семь 32-бит регистров для записи и хранения сообщений. Модуль формирует прерывания, которые могут адресоваться любому из трех процессоров или одновременно всем.

В МК встроена память SRAM с кодом коррекции ошибок ECC емкостью 2 Мбайт. у других модификаций семейства объем SRAM может достигать 6 Мбайт. Для работы с внешней памятью DDR2/3 в МК используется специальный контроллер. Благодаря многопортовой архитектуре удается эффективно распределить доступ к памяти разных типов. Перечислим некоторые особенности контроллера DDR2/3:

- контроллер работает асинхронно с сетью NoC;

- величина адресного пространства (макс.): 2 Гбайт;

- ширина шины данных: 8 или 16 бит и 8-бит ECC;

- схема приоритетов задается программно;

- входящий адрес и тип команды для каждого порта проверяется, как указано в установочном регистре;

- можно сформировать до 16 областей адресного пространства, каждая из которых проверяется по своему правилу.

Контроллер DDR2/3 преобразует адреса пользователя в адреса памяти. Размер используемой памяти DDR2/3 необходимо записать в установочный регистр. Структура адреса памяти состоит из пяти полей, к каждому из которых можно адресоваться отдельно. Вся цепочка выглядит следующим образом: «Выбор кристалла – строка – банк – столбец – тракт передачи данных».

Контроллер флэш-памяти NAND, как нетрудно догадаться, реализует обмен данными с памятью NAND. Формат данных соответствуют требованиям спецификации ONFI 2.2 и более ранней ONFI 1.x. Контроллер может работать в асинхронном режиме и поддерживает до четырех микросхем NAND. Контроллер реализует защиту памяти, поддерживает страницы объемом 356 байт…16 Кбайт.

Для коммутации с памятью используется встроенный контроллер Quad SPI, который также адресуется к четырем микросхемам, поддерживает 1/2/3/4-байт адресацию и осуществляет защиту записи. Заметим, что контроллер не осуществляет декодирование адресов, а входящие адреса и есть адреса флэш-памяти.

В состав МК входят два контролера SDIO/SD/eMMC, каждый из которых реализует многоблочные циклы записи/стирания. Скорость передачи данных при тактировании частотой 25 МГц составляет 12,5 Мбит/с, а в высокоскоростном режиме при тактировании частотой 50 МГц скорость передачи данных увеличивается до 25 Мбит/с. Передача данных производится в формате 1, 4 или 8 бит. Интерфейс USB соответствует стандарту USB 2.0, тактируется частотой 48 МГц и поддерживает скорости передачи данных 480 Мбит/с, 12 Мбит/с (USB 1.1), 1,5 Мбит/с (USB 1.1).

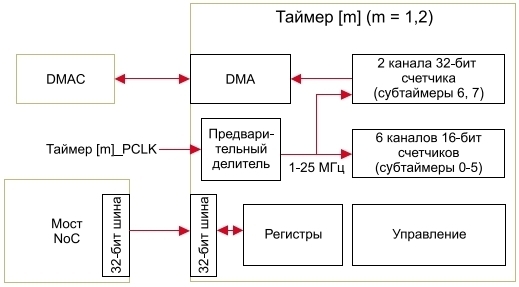

Рисунок 4

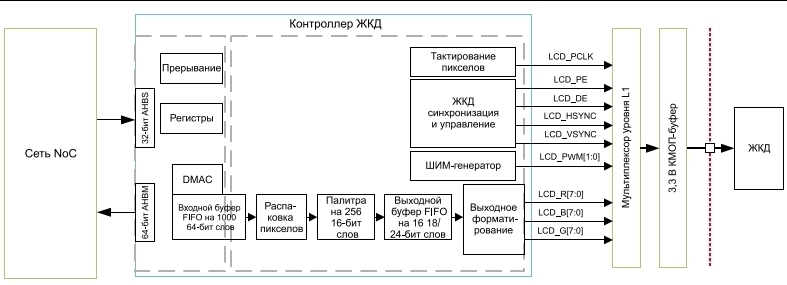

Рисунок 5

Структурная схема блока таймеров

Структурная схема контроллеру ЖКД

Периферия

В состав периферийных модулей входят коммуникационные интерфейсы, порты ввода/вывода, интерфейс внешней шины MSEBI, АЦП, модули таймеров и контроллер ЖКД. К коммуникационным интерфейсам отнесем следующие:

– 8×UART. Максимальная скорость передачи данных каждого порта достигает 5,2 Мбит/с, каждый порт имеет отдельные буферы FIFO 16×8 на прием и передачу данных;

– SPI. Четыре ведущих порта и два ведомых, длина кадра 4–1 бит, буферы FIFO 16×16;

– 2×I2C. В стандартном режиме скорость передачи данных до 100 Кбит/с, в высокоскоростном режиме – до 400 Кбит/с; 7- или 10-бит адресация, буферы FIFO 8×8;

– 2×CAN. Скорость передачи данных 125 Кбит/с… 1 Мбит/с, 11- и 29-бит идентификаторы.

Интерфейс внешней шины MSEBI полностью программируется и может работать как ведущее, так и ведомое устройство. Возможно обращение к четырем внешним синхронным или асинхронным устройствам одновременно (четыре линии chip select). 32-бит шину данных можно сконфигурировать в 8- или 16-бит шину.

В состав МК входят три базовых модуля порта ввода/вывода BGPIO, на основании которых конфигурируются шесть отдельных портов ввода/вывода. Прерывания от них можно формировать не только по уровню входного сигнала, но и по его фронту.

Немного подробнее остановимся на блоке таймера. Его структурная схема показана на рисунке 4. Поскольку рисунок исчерпывающе иллюстрирует функциональные возможности блока, мы добавим лишь несколько уточнений фраз. В состав МК входят два идентичных блока, каждый из которых содержит два программируемых 32-бит таймера и шесть программируемых 16-бит таймеров.

Таймеры могут работать в режиме автоматической перезагрузки; при этом при переполнении содержимое таймера сбрасывается, и отсчет начинается заново. В режиме автоматической перезагрузки могут формироваться прерывания при достижении установленного значения счета. В режиме однократного счета при достижении заданного значения счетчик таймера останавливается, и генерируется прерывание.

Стоит уделить несколько большее внимание контроллеру ЖКД со структурной схемой на рисунке 5. Под интерфейс ЖКД выделен один порт; можно использовать 18-бит формат (6 бит на цвет) или 24-бит формат (8 бит на цвет). При использовании цветовой палитры возможен формат 1, 2, 4, 8 бит/пикс. Цветовая палитра содержит 256 16-бит слов. яркость подсветки регулируется ШИМ-генератором. Входной буфер FIFO имеет емкость 1000 64-бит слов, а выходной – 16 24-бит слов.

Контроллер инициализируется непосредственно процессорным ядром. Первоначально необходимо запрограммировать как минимум регистры вертикальной и горизонтальной синхронизации и регистр тактирования пикселов, а также вписать базовые адреса в регистры DMA. При использовании цветовой палитры ее необходимо сначала загрузить.

Старт передачи кадра осуществляется по внутреннему импульсу синхронизации, совпадающему с импульсом вертикальной синхронизации. При этом начинается загрузка данных из буферной памяти через каналы DMA и распаковка пикселов. Через ведущий интерфейс осуществляется чтение шиныAHB. В течение одного обращения может быть считан пакет из 4, 6 или 16 64-бит слов. Они записываются во входной буфер FIFO. В дальнейшем слова распаковываются и передаются через палитру в выходной буфер FIFO.

Контроллер может управлять дисплеями размерностью от QVGA (320×240 пикс.) до XGA (1024 768 пикс.). При этом при частоте 60 кадров/с скорость передачи данных находится в пределах 0,6 Мбайт/с (QVGA, 1 бит/пикс.) – 188,7 Мбайт/с (XGA, 18/24 бит/пикс.).

Обзор модулей периферии закончим кратким описанием АЦП. В состав МК входят два модуля 12-бит АЦП последовательного приближения. Их производительность находится в пределах 0,0625–1 Мвыб/с. Время преобразования не превышает 21 тактового импульса АЦП, частота тактирования находится в диапазоне 2–20 МГц. Оба модуля АЦП имеют по восемь входных каналов, каждый из которых может запускаться отдельно. Максимальная дифференциальная нелинейность преобразования составляет ±1 МЗР, а максимальная интегральная нелинейность не превышает ±4 МЗР.

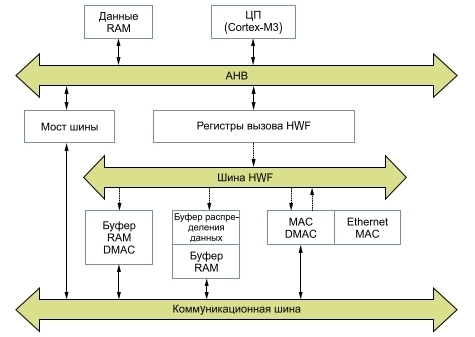

Рисунок 6

Модуль аппаратной реализации функций (HWF) Ethernet

R-IN Enginе и Ethernet

R-IN Engine – фирменная аппаратная технология компании Renesas, ускоряющая работу операционной системы. Она поддерживает разные сетевые технологии и ускоряет обмен данными по TCP/IP, а за счет снижения нагрузки на процессорные ядра еще и уменьшает энергопотребление. В традиционных решениях все процессы, связанные с контроллером Ethernet, выполняются процессором в операционной системе реального времени.

Технология R-IN значительно разгружает процессор и ускоряет обработку с помощью аппаратных средств. В отличие от использования процессора, обеспечивается стабильная, без задержек, обработка данных и управление контроллерами Ethernet. Фактически технология R-IN Engine аппаратными средствами частично реализует RTOS (HW RTOS). В МК RZ/N1D в состав R-IN входят следующие компоненты:

– Cortex-М3 с контроллером векторных прерываний, обрабатывающий до 126 прерываний;

– SRAM емкостью 2 Мбайт, из которых 1 Мбайт отведен под память данных и 1 Мбайт предназначен для хранения команд;

– HW RTOS, реализующая управление ресурсами встроенным DMA и контроллером GMAC;

– одноканальный контроллер GMAC с интерфейсом GMII.

Перечислим некоторые основные особенности HW RTOS;

– 30 системных вызовов аналогичных вызовам в RTOS ITRON;

– обработка 32 прерываний;

– 64 контекстных регистр, 16 уровней

– 64 контекстных регистр, 16 уровней приоритета;

– 64 события и 64 почтовых ящика.

К R-IN Engine также относится контроллер Gigabit Ethernet MAC (HW-RTOS GMAC) с одним портом, обеспечивающий скорость передачи данных 1 Гбит/с и полнодуплексную связь; кроме того, контроллер управляет 5-портовым коммутатором A5PSW. В МК встроен модуль аппаратной реализации функций (HWF) Ethernet, структурная схема которого показана на рисунке 6. В его задачу входит распределение ресурсов, управление MAC DMA, буферизация данных RAM DMA.

Буфер распределения данных управляет буферизованной памятью RAM, которая, в свою очередь, используется для увеличения пропускной способности Ethernet. Несмотря на то, что емкость буфера RAM составляет 128 Кбайт, в адресном пространстве ему отведено 128 Мбайт, что позволяет использовать динамическое перераспределение памяти. Контроллер MAC DMA осуществляет передачу данных между буферной памятью RAM и Ethernet MAC, позволяя увеличить пропускную способность канала передачи данных.

Коммутатор A5PSW, управляющий пятью портами, применяется только при работе в полнодуплексном режиме со скоростью передачи данных 1000 Мбит/с. При этом передача данных соответствует требованиям стандарта IEEE 1588–2008. При тактировании коммутатора частотой 200 МГц скорость передачи через каждый из четырех портов достигает 1000 Мбит/с, а пятый порт используется для управления.

Ведомый контроллер EtherCAT соответствует спецификации ETG.1000 EtherCAT. Некоторые параметры контроллера EtherCAT:

- поддержка до трех портов;

- восемь модулей управления памятью интерфейса Fieldbus FMMU;

восемь SyncManagers для защиты областей памяти от одновременного доступа;

- объем RAM данных: 8 Кбайт;

- защита записи.

Заметим, что на физическом уровне не рекомендуется использовать RMII. Поскольку в состав этого интерфейса входят буферы FIFO в передающем канале, которые увеличивают задержку переадресации и джиттер, предпочтительнее использовать MII.

Два контроллера Gigabit Ethernet GMAC отвечают требованиям стандартов IEEE 802.3–2008, IEEE 1588–2008 v2, IEEE-C37.238, IEEE 802.3-az. vD2.0. Поскольку этот интерфейс хорошо известен, мы не будем останавливаться на его описании, но перечислим некоторые из его основных параметров:

- скорость передачи данных: 10/100/1000 Мбит/с;

- режим передачи данных: дуплексный и полудуплексный;

- программируемая длина кадра: до 16 Кбайт;

- поддержка большого числа режимов фильтрации адресов, передача кадров без фильтрации;

- пробуждение по сети LAN или особым пакетом (magic packet).

Контроллер GMAC 1 и GMAC подключаются к внешним портам 1 и 2, соответственно, через RGMII/RMII. Инициализация GMAC должна осуществляться после инициализации DMA. При несоблюдении этого условия происходит переполнение буфера FIFO в канале приема данных.

Коммутатор бесшовного резервирования среды высокой готовности (HSR) соответствует требованиям стандарта IEC 62439–3:2016. Скорость передачи данных в дуплексном режиме составляет 100 Мбит/с. Другие варианты не поддерживаются. Задержка передачи данных не превышает 960 нс. Возможна коммутация со 128 внешними узлами; при этом размер кадра достигает 2 Кбайт. Временная синхронизация отвечает требованиям стандарта IEEE 1588–2008. Физический уровень – MII.

Последовательный коммуникационный интерфейс реального времени Sercos III известен более 30 лет. В МК применяется ведомый контроллер Sercos III IP версии 4.12.0. Он имеет два порта и реализует передачу данных со скоростью 100 Мбит/с. Для управления и хранения данных используется двухпортовое ОЗУ. Обрабатываются только данные, предназначенные для конкретного пользователя. Передача данных из RAM осуществляется в течение нескольких циклов тактирования. Через мультиплексор допускается переключение между протоколами Sercos и Ethernet. Физический уровень – MII.

Приложения отправляют и получают данные через интерфейс ввода/вывода данных MDIO. Этот двухпроводной интерфейс позволяет приложению получить доступ к любым регистрам PHY, а также выбрать любой из 32 PHY и любой из 32 регистров этого PHY. Однако в каждый момент времени можно осуществить обращение только к одному регистру.

Выводы

В статье относительно детально рассмотрены микроконтроллеры RZ/N1D семейства RZ/N. Привлекательной особенностью этих МК является технология R-IN Engine, позволяющая ускорить коммуникационные процессы с промышленными устройствами через сеть Ethernet. Дополняют связные возможности МК 18 стандартных коммуникационных интерфейсов. учитывая, что эти МК могут управлять ЖКД размерностью от QVGA до XGA, эти устройства предназначены для широкого ряда систем промышленной автоматизации.

Корзина пуста

0

шт.

/

$0

Оформить

Очистить