- 8 (812) 612-97-27

- СПБ, Курчатова дом 1А помещение 1Н

- order@das-elektro.de

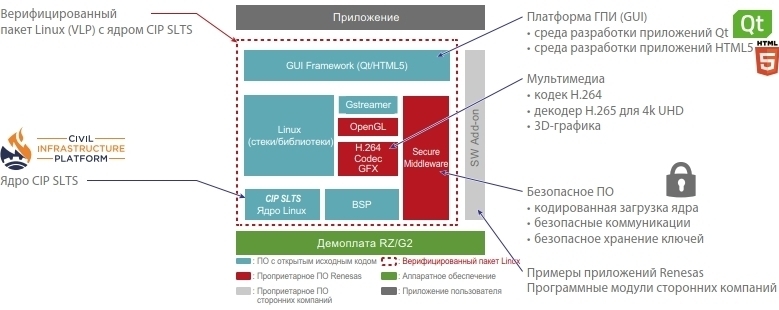

МИНИАТЮРНЫЙ КВАРЦЕВЫЙ ГЕНЕРАТОР ПОВЕРХНОСТНОГО МОНТАЖА С ЦИФРОВОЙ ТЕРМОКОМПЕНСАЦИЕЙ

В статье кратко описаны микроконтроллеры семейства RZ/G2 от компании Renesas Electronics. Основное внимание уделено самой производительной микросхеме – RZ/G2H. Микроконтроллеры имеют отличные мультимедийные возможности и могут использоваться для создания расширенного человеко‑машинного интерфейса. Вычислительные возможности микроконтроллеров позволяют применять их в самых сложных встраиваемых системах управления и на всех уровнях АСУ.

Введение

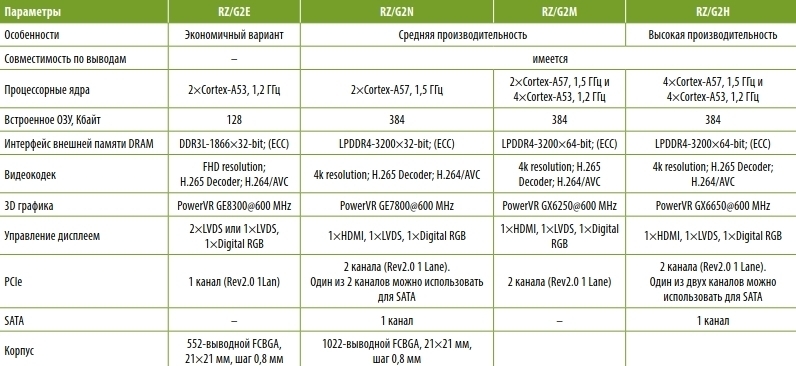

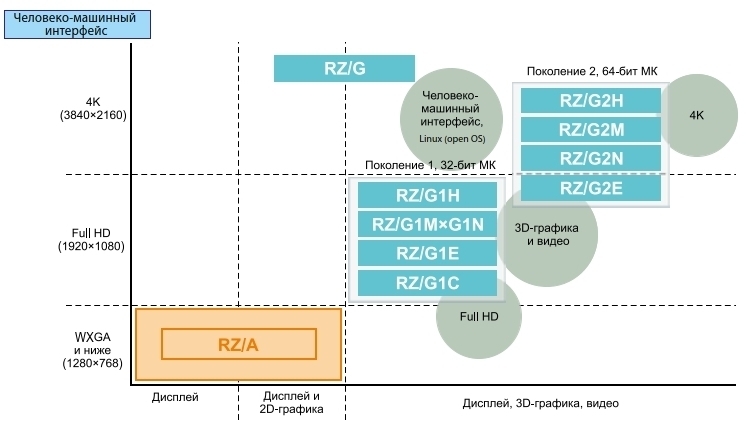

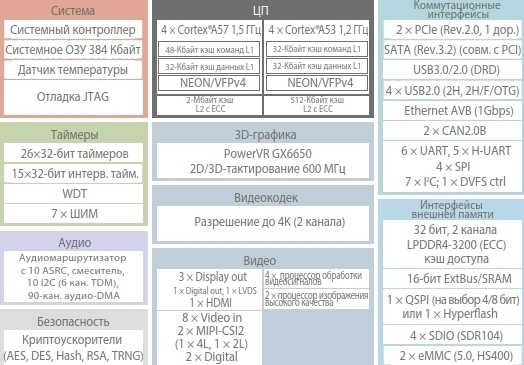

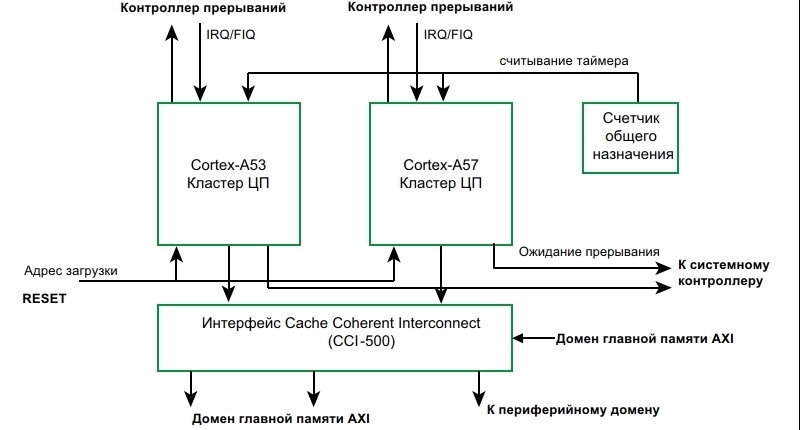

Компания Renesas Electronics в очередной раз пополнила свою производственную линейку микроконтроллеров (МК) семейством RZ/G2. Главным отличием нового многоядерного семейства является использование 64-бит архитектуры Arm v8-A с процессорными ядрами Cortex-A53 и Cortex-A57. МК нового семейства можно использовать во встраиваемых системах, для автоматизации зданий, на всех уровнях АСУ. На их основе можно создавать человеко-машинный интерфейс нового поколения. В состав семейства входят четыре группы МК. Их основные различия и параметры приведены в таблице 1. Одним из главных приложений МК этого семейства является человеко-машинный интерфейс с расширенными графическими возможностями. На рисунке 1 иллюстрируются графические возможности МК семейств RZ. Возможность МК семейства RZ/G2 управлять дисплеями 4K выгодно выделяет их из ряда конкурентов. Еще одним преимуществом рассматриваемых МК является долговременная поддержка платформы разработки Civil Infrastructure Platform (CIP) со временем обслуживания более 10 лет. Попутно заметим, что ядро CIP SLTS Linux поддерживает безопасность и уменьшает уязвимость системы. Структурная схема платформы разработки МК семейств RZ/G представлена на рисунке 2. В дальнейшем изложении мы, в основном, будем ссылаться на МК RZ/G2H с наибольшей производительностью. Однако основное отличие этого МК заключается в вычислительных возможностях, благодаря четырем ядрам Cortex-A57 и четырем ядрам Cortex-A53. Остальные различия не существенны. Ядра Cortex-A57 тактируются частотой 1,5 ГГц, а ядра Cortex-A53 – частотой 1,2 ГГц. Структурная схема МК RZ/G2H приведена на рисунке 3.

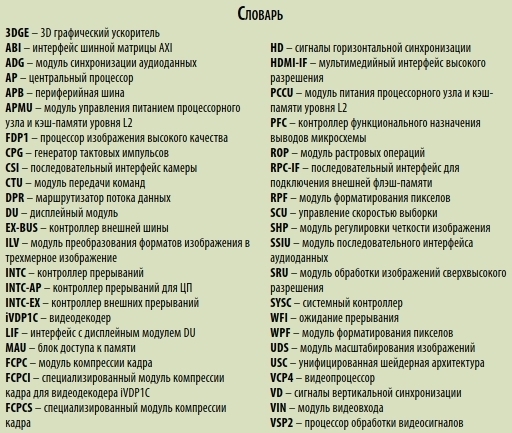

Таблица 1

Основные различия и параметры МК семейства RZ/G2

Рисунок 1

Рисунок 2

Графические возможности человеко-машинного интерфейса с МК семейства RZ/G

Структурная схема платформы разработки МК семейств RZ/G

Рисунок 3

Структурная схема МК RZ/G2H

Процессорный узел АР и память

Структурные схемы процессорных ядер и подробное описание их работы можно найти на сайте компании arm. Мы ограничимся тем, что приведем некоторые их основные параметры, которые, на наш взгляд, должны дать достаточное представление о функциональных возможностях и производительности ядер. Начнем с ядра Cortex-A53:

- тактовая частота (макс.): 1,2 ГГц;

- кэш-память команд уровня L1: 32 Кбайт;

- кэш-память данных уровня L1: 32 Кбайт;

- кэш-память данных уровня L2: 512 Кбайт;

- поддержка векторного сопроцессора NEON/VFP;

- поддержка кода коррекции ошибок ECC;

- встроенный модуль защиты памяти MMU;

- режимы пониженного энергопотребления.

Далее перечислим некоторые параметры процессорного ядра Cortex-A57:

- тактовая частота (макс.):

1,2 ГГц; - кэш-память команд уровня L1: 48 Кбайт;

- кэш-память данных уровня L1: 32 Кбайт;

- кэш-память данных уровня L2: 2 Мбайт;

- поддержка векторного сопроцессора NEON/VFP;

- поддержка кода коррекции ошибок ECC;

- встроенный модуль защиты памяти MMU;

- режимы пониженного энергопотребления. Интересной особенностью является когерентное соединение кэш-памяти, которое совмещает функции когерентности кэша и межсоединения. Структурная схема процессорного узла (АР) представлена на рисунке 4. Отдельный модуль управления питанием APMU процессорного узла и кэш-памятью уровня L2 реализует четыре режима энергопотребления процессорного узла АР (см. табл. 2). Помимо кэша-памяти, во всех МК R Z /G2 кроме МК RZ/G2E имеется встроенное ОЗУ объемом 384 Кбайт. Память тактируется частотой 400 МГц, ширина шины – 512/236/128 бит. В экономичной модификации МК RZ/G2E емкость ОЗУ меньше и составляет 128 Кбайт. Для подключения внешней памяти используются следующие встроенные интерфейсы. – EX-BUS с 16-бит шиной и частотой тактирования 66 МГц. Поддерживает внешние ОЗУ и ПЗУ. – RPC–IF с частотой тактирования до 180 МГц. Поддерживает до двух модулей внешней последовательной флэш-памяти со скоростью передачи данных 160 Мбит/с для каждого модуля памяти. Суммарная скорость передачи данных – 320 Мбит/с. – Контроллер внешней шины для подключения памяти LPDDR4–3200. Два канала с шириной шины по 32 бит. Суммарный объем подключаемой памяти – до 8 Гбайт. Заметим, что LPDDR4X (JESD209–4-1) не поддерживается.

Таблица 2

Режимы энергопотребления процессорного узла АР

Рисунок 4

Рисунок 5

Структурная схема процессорного узла

Структурная схема видеопроцессора VCP4 и его связь с другими модулями

Рисунок 6

Структурная схема процессора FDP1

Мультимедиа и графика

В качестве графического ускорителя (3DGE) в МК RZ/G2H используется PowerVR GX6650 на частоте 600 МГц. Архитектура ускорителей PowerVR Series6XT базируется на Series6. На текущий момент, в т. ч. благодаря использованию графического интерфейса OpenGL ES, эта архитектура имеет наилучший показатель в отрасли по соотношению энергопотребления к занимаемой площади (мВт/мм2). К тому же, эта архитектура отлично масштабируется и может поддерживать до восьми вычислительных кластеров. К основным особенностям ускорителя 3DGE относятся следующие:

- улучшенная визуализация с одновременной обработкой нескольких сегментов;

- многопоточный механизм с унифицированной шейдерной архитектурой USC;

- в архитектуру USC входит АЛУ, что позволяет поддерживать векторную обработку (SIMD);

- полная виртуализация адресации памяти позволяет поддерживать унифицированную архитектуру памяти;

- мелкоструктурная обработка позволяет переключаться между задачами для балансировки нагрузки и упрощение управления питанием;

- программируемое сглаживание изображений;

- компрессия текстур и параметров без потерь.

В МК встроены два последовательных интерфейса камеры CSI2 на две и четыре линии. Поддерживаются стандарты MIPI CSI-2 V1.1 и MIPI D-PHY V1.1. В состав модуля CSI2 входят PHY и LINK. Модуль PHY принимает сигналы, отделяет данные изображения от служебной информации и передает их модулю LINK, который формирует сигналы вертикальной синхронизации VD, горизонтальной синхронизации HD и т. д. у модуля LINK имеется интерфейс периферийной шины APB, у модуля LINK такового нет. Заметим, что скорость передачи данных от камеры не должна превышать 1,5 Гбит/с, т. к. превышение приведет к потере данных.

Модуль видеовхода VIN производит захват видеоданных, которые передаются во внешнюю память. Данные в формате YCbCr-422 передаются через интерфейсы ITU-R BT.601, ITU-R BT.656 или ITU-R BT.709, данные в формате RGB – через интерфейсы ITUR BT.601 или ITU-R BT.709. Модуль имеет восемь независимых каналов, по каждому из которых может осуществляться захват изображения размерностью 4096×4096 пикс. Данные формата YCbCr-422 преобразуются в формат RGB. В режиме однократного захвата происходит захват одного кадра, а в режиме непрерывного захвата – всех поступающих кадров.

Видеодекодер iVDP1C осуществляет декодирование изображений до размерности 1920×1080 при скорости 60 кадр./с или 120×960 при 120 кадр./с. Процесс происходит с малой задержкой и обеспечивает высокую точность воспроизведения форматов стандартов H.264/AVC и JPEG. Максимальная скорость составляет 40 Мбит/с при четырех потоках или 160 Мбит/с – при одном.

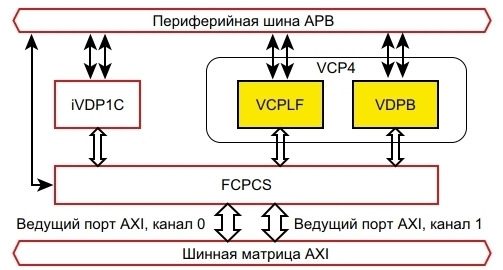

Видеопроцессор VCP4 представляет собой набор нескольких кодеков, осуществляющих кодирование и декодирование нескольких видеофайлов форматов H. 265/HEVC , H. 26 4/AVC. В состав VCP4 входят два ядра: VDPB и VCPLF. ядро VDPB предназначено для декодирования H.265/HEVC, а VCPLF реализует операции кодирования и декодирования с несколькими кодеками. На рисунке 5 представлена структурная схема видеопроцессора VCP4 и его связь с другими модулями.

Производительность видеопроцессора в формате H. 265 составляет 3840×2160 при 60 кадр./с или 1920×1080 при 120 кадр./с. Скорость обработки данных ядром VCPLF составляет 30 Мбит/с по каждому из четырех потоков или 120 Мбит/с – по одному. Если входной поток не соответствует стандарту видеокодеков, возможно их зависание.

Процессор обработки видеосигналов VSP2 поддерживает 1D и 3D таблицы преобразования, масштабирование, поворот и сшивку изображений, интерфейс с дисплейным модулем (DU).В состав процессора VSP2 входит несколько модулей. Все они осуществляют обработку по принципу «память–память», не используя ресурсы ЦП.

Модуль VSPI осуществляет масштабирование и вращение изображения. Модуль VSPBC реализует таблицы преобразования, построение 1D-гистограмм и сшивку изображений. Модуль VSPBD осуществляет сшивку изображений, а модуль VSPD помимо сшивки изображений реализует интерфейс с дисплейным модулем. Приведем некоторые основные численные параметры процессора обработки видеосигналов VSP2: - обрабатываются форматы: YCbCr444/422/420, RGB, α RGB; - размерность обрабатываемого изображения (макс.) : 3840×2160 пикс.;

- производительность: два канала по 500 Мпикс./с; - при прямом подключении к дисплейному модулю передача до 4096 пикс. по горизонтали.

Работу в режиме «память–память» обеспечивает модуль доступа к памяти MAU. Он является ведущим блоком шины, загружая данные из внешней памяти, а после завершения обработки вновь передает их во внешнюю память. Модуль передачи команд CTU может обращаться непосредственно к регистрам и считывать параметры обработки изображения. Модуль растровых операций (ROP) выполняет операции наложения изображений, а при необходимости модуль цветовой кодировки заменяет цвет.

Модуль форматирования пикселов RPF считывает данные обрабатываемого фрагмента из внешней памяти, извлекает данные из архива, выполняет цветовые конвертации. Модуль форматирования пикселов WPF получает 32-бит данные изображения (YCbCr444 или RGB888 + 8bit-α) и преобразует цветовое пространство, цветность и формат данных, а также передает результаты обработки изображения во внешнюю память через модуль MAU.

Маршрутизатор DPR управляет потоками данных между модулем RPF, функциональными модулями и WPF. Он, в частности обеспечивает непрерывность обработки изображения без использования внешней памяти за счет перенаправления данных между функциональными модулями. Отметим еще модуль SRU, который обеспечивает обработку изображений сверхвысокого разрешения, и модуль масштабирования изображений UDS.

Описание видеопроцессора VCP4 завершим упоминанием функциональных модулей SHP, ILV и служебного модуля LIF, обеспечивающего интерфейс с дисплейным модулем DU. Модуль SHP регулирует резкость изображения, а ILV преобразует форматы изображения в трехмерное изображение.

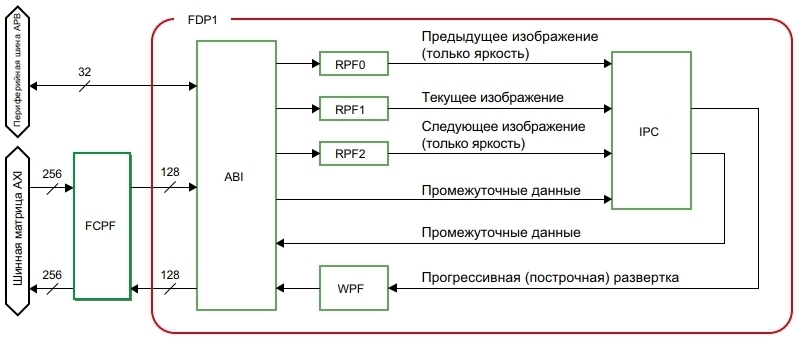

Двухканальный процессор изображения высокого качества FDP1 преоб- разует видеоданные с чересстрочной разверткой в данные с прогрессивной (построчной) разверткой. Процессор извлекает данные из внешней памяти и после обработки передает обработанные данные во внешнюю память. Трансфер данных осуществляется модулем ABI, который представляет собой интерфейс шинной матрицы AXI.

Структурная схема процессора FDP1, представленная на рисунке 6, лучше всяких слов скажет о его устройстве, поэтому мы лишь приведем некоторые основные параметры процессора FDP1:

- размер изображения (макс.): 8190×8190 пикс.;

- скорость обработки данных: 500 Мпикс./с;

- цветовые форматы (вход):

- YCbCr444-PL, SP, ILV;

- YcbCr422-PL, SP, ILV;

- YCbCr420-PL, SP;

- размер кадра (мин.): 32×32 пикс.;

- цветовые форматы (выход): RGB и YCbCr.

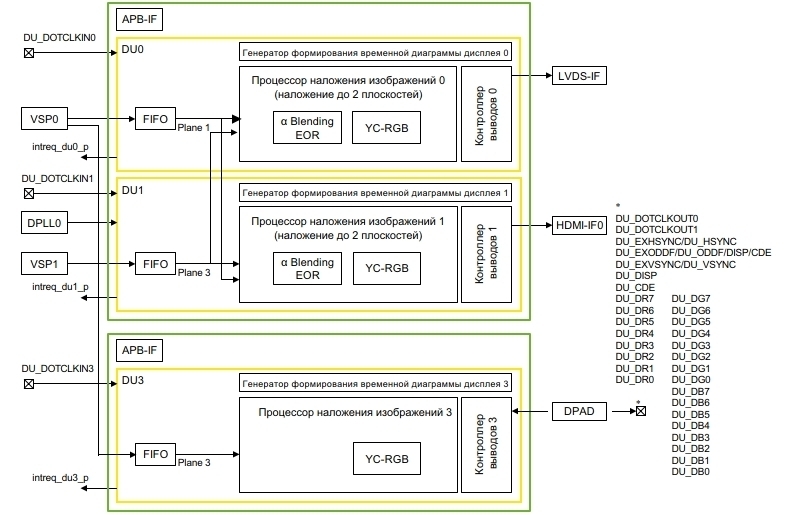

На вход дисплейного модуля DU поступают выходные сигналы процессора обработки видеосигналов VSP2. На выходе дисплейного модуля формируются сигналы для передачи на дисплей через интерфейсы LVDSIF, HDMI–IF, цифровой RGB. Структурная схема модуля DU показана на рисунке 7. Модуль может управлять тремя дисплейными панелями, причем возможно наложение изображений двух панелей. управление каждой из них происходит раздельно. Параметры управления каждой панелью прописываются во внутренних регистрах дисплейного модуля. В этих же регистрах выбирается одна из трех временных диаграмм управления и режимы развертки. В них же задаются параметры цветового преобразования и ряд других установок.

Аудиомодуль имеет выделенные каналы DMA – Audio-C, Audio-DMACpp. Он непосредственно соединен с модулем синхронизации аудиоданных ADG и модулем последовательного интерфейса аудиоданных SSIU. В состав модуля не входят собственные регистры. Каналы Audio-DMACpp осуществляют связь между аудиомодулем и внешней памятью.

Рисунок 7

Структурная схема модуля DU

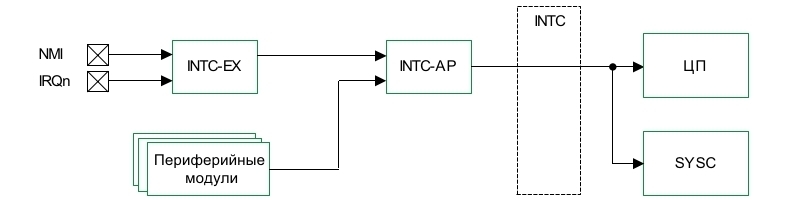

Рисунок 8

Соединение контроллеров прерывания

Прочие ресурсы МК

В этом коротком разделе упомянем некоторые модули МК, которые не вошли или имели другие функциональные возможности в составе других семейств. Контроллер функционального назначения выводов микросхемы PFC состоит из регистров, в которых прописываются назначения мультиплексированных выводов, а также управление (подключение к шине питания или земле) подтягивающих резисторов линий ввода/вывода. Системный контроллер SYSC управляет питанием процессорного узла, модулей 3D-графики, видеопроцессором, модулями видеокодеков. Если какие-то из перечисленных модулей не активны, контроллер отключает их питание, за счет чего снижается энергопотребление. Отключение питания – более действенный способ, чем прекращение тактирования, т. к. в последнем случае сохраняются токи утечки. Кроме того, контроллер SYSC управляет последовательностью включения и выключения модулей. Разумеется, при выключении питания модуля прекращается его тактирование. В МК используются три контроллера прерывания: контрол- лер внешних прерываний INTC-EX, контроллер прерываний для цП INTC-AP и системный контроллер прерываний INTC. Их взаимодействие показано на рисунке 8. Контроллер прерываний INTC-AP интегрирован во внутреннюю сеть Arm CoreLink GIC-400 (r0p0). Он обрабатывает прерывания системного домена и имеет 32 программных уровня приоритета. Как нетрудно догадаться, контроллер INTC-EX обрабатывает прерывания от внешних устройств, поэтому на его входах для шумоподавления установлен антидребезговый фильтр. В МК встроены широко известные коммуникационные интерфейсы. Мы отметим только наличие интерфейсов PCIe и SATA, которые отнюдь не часто встречаются в микроконтроллерах. Совместно со встроенным интерфейсом Ethernet 1 Gbit они позволяют использовать МК в самых сложных встраиваемых системах управления и на всех уровнях АСУ.

Корзина пуста

0

шт.

/

$0

Оформить

Очистить